SPRAA56

DSP/BIOS Real-Time Analysis (RTA) and Debugging Applied to a Video Application 15

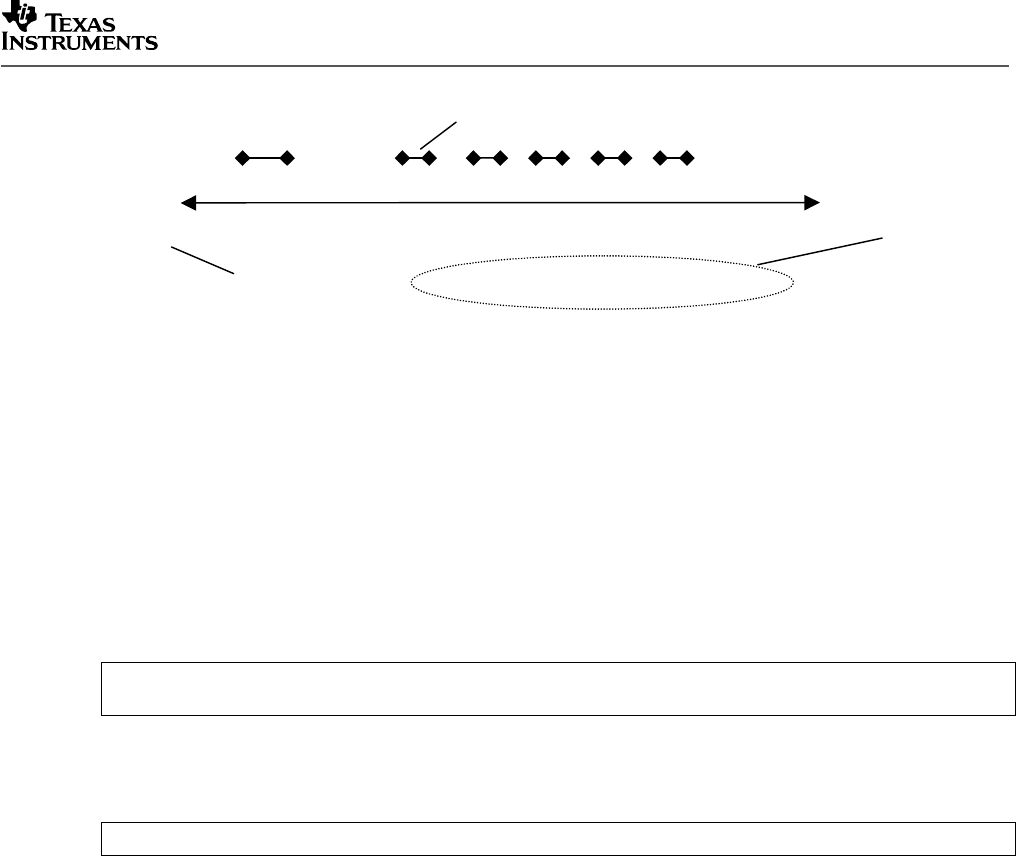

Window = 500ms

(

default

)

t0 t1 t0 t1

‘

minloo

p

’

(

in units of ~ c

y

cles

)

‘count’ is # hits of

LOAD_idlefxn in the

window

c

p

uload =

(

100 -

((

100 *

(

count * minloo

p))

/ total

))

IDL load

100 – IDLload gives

App

CPU Load

Figure 4. CPU Load Measurement at Run-Time

The LOAD module relies on an IDL thread to be inserted in an application to calibrate the

amount of time needed to run a single iteration of the DSP/BIOS idle loop. It estimates the CPU

load by dividing the idled time by the time elapsed and subtracting the result from 1. The load is

multiplied by 100 and reported as a percentage.

To use the LOAD module in a project, follow these steps:

1. Configure an IDL function that calls LOAD_idlefxn. This routine runs in the background to

measure the time spent in the CPU’s IDL (background) loop and compares it with the time

spent outside the background loop to calculate a CPU load. The following Tconf statements

configure such an object.

var CpuLoadCheck = tibios.IDL.create("CpuLoadCheck");

CpuLoadCheck.fxn = prog.extern("LOAD_idlefxn");

2. Include load.c and load.h in the project.

3. Call LOAD_getcpuload as needed within your application:

thrProcRta.cpuLoad = LOAD_getcpuload();

The project keeps track of the number of times the idle loop is entered over a time period

specified by the “window” variable in load.c. The CPU load reported by LOAD_getcpuload is the

load during the previous window period. You can modify the value of the "window" variable to

suit the variability of the CPU load in your application.

Because the LOAD_idlfxn routine is only called during the background loop, while all other tasks

in the system are presumably blocked or not ready, the only load introduced by this module is

the execution time of the call to LOAD_getcpuload, which is approximately 1200 instruction

cycles.

4.7 Memory Bus Utilization

Processor utilization is a measurement of the DSP resources consumed by a given task,

algorithm, or function. It is more than just MIPS consumption, however, since memory bus

utilization is an important component of processor utilization, particularly when working with

high-resolution video (greater than 720x480).