TC9457F

2002-10-21

6

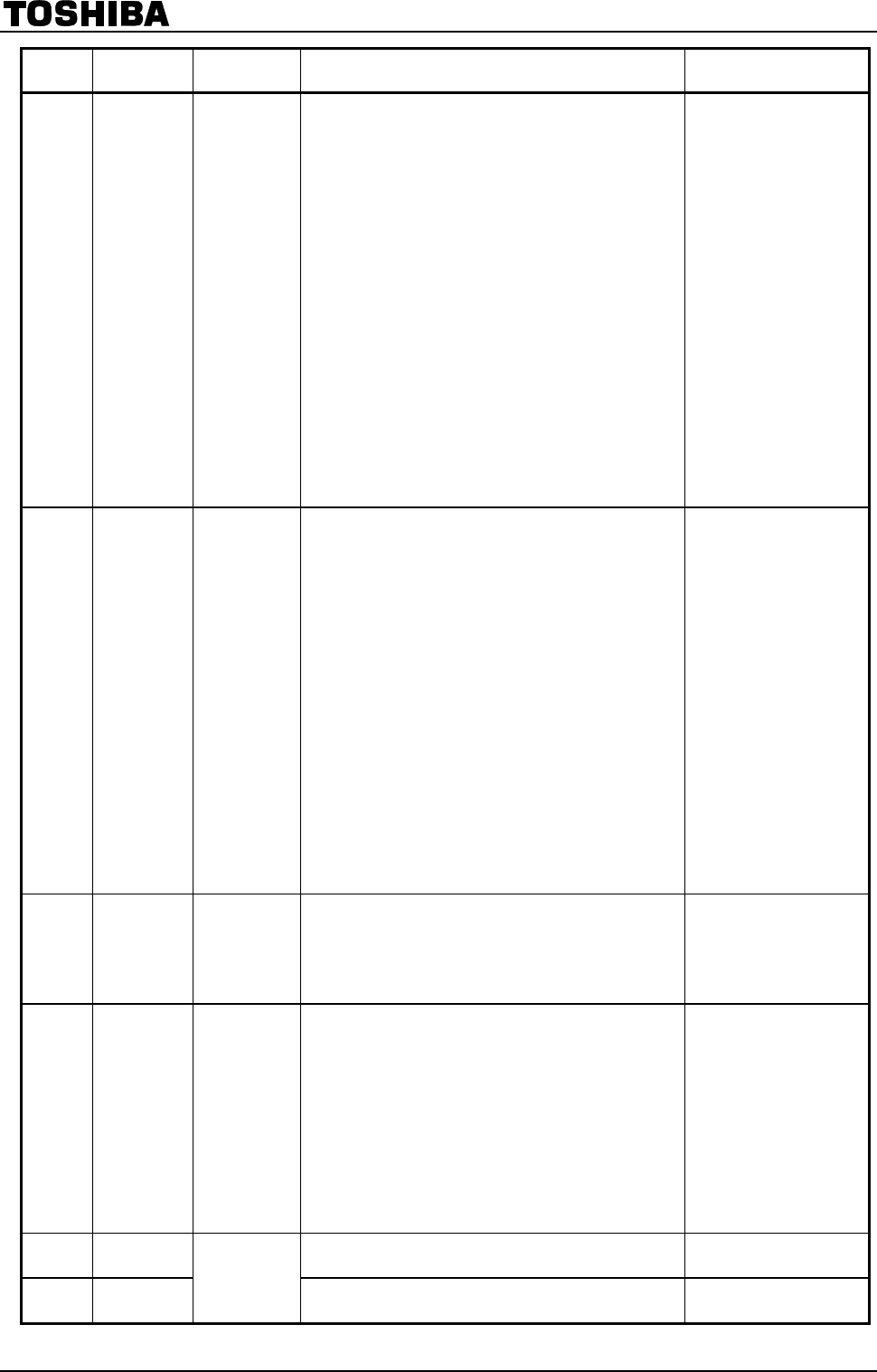

Pin No. Symbol Pin Name Function And Operation Remarks

25

26~28

29

P3-0/DCREF

P3-1/ADIN1

~

P3-3/ADIN3

P4-0/ADIN4/

BUZR

I/O port 3

/AD analog

reference

voltage input

I/O port 3

/AD analog

voltage input

I/O port 4

/AD analog

voltage inputs

/Buzzer output

5-bit CMOS I/O ports.

These ports can be set for input or output bit for bit by a

program.

The P3-0 to P4-0 pins serve dual purposes as analog

inputs for the internal 6-bit 4-channel AD converters.

The internal AD converters can complete conversion in 6

instruction cycles using a successive approximation

method. The required pins can be set for AD analog input

bit for bit by a program. P3-0 can be set for reference

voltage input, and the internal power supply (MV

DD

) can

be used for this reference voltage.

The P4-0 pin serves dual purposes as a buzzer output

pin.

The buzzer output can be selected from 8 frequencies,

0.625 to 3 kHz. Each selected frequency can be output in

one of four modes: continuous, single, 10 Hz intermittent,

and 10 Hz intermittent at 1 Hz interval.

Whether or not to use and how to control the AD converter

and buzzer all can be set by a program.

Note 2: If P3-0 is set for reference voltage input, note that

although normally in a high-impedance state, this

input during AD conversion becomes a 10 kΩ

load, typ. Therefore, pay careful attention to the

output impedance that is input to this pin.

―

30

31

32

P4-1/S12

P4-2/S0/SI1

/SDA

P4-3/SCK

/SCL

I/O port 4

/Serial data

input

/Serial data

input /output

/Serial clock

input /output

3-bit CMOS I/O ports.

These ports can be set for input or output bit for bit by a

program.

These pins serve dual purposes as input or output pins for

the serial interface circuit (SI0).

The SI0 is a 2-wire/3-wire compatible serial interface.

4 or 8 bits of serial data, beginning with the MSB or LSB,

are serially output from the SO/SDA pin at each clock

edge on the SCK/SCL pin, and the data on SI1 or SI2 pin

is serially input to the device. The serial clock (SCK/SCL)

allows selection between the internal (450/225/150/75

kHz) and external sources and a selection of the active

edge, rise or fall. Moreover, since the clock and data can

be output via Nch open-drain outputs, various device

controls and communication between controllers can be

greatly facilitated.

When an SI0 interrupt is enabled, an interrupt is

generated at completion of SI0 execution and the program

jumps to address 4. This is effective when high-speed

serial communication is desired.

All inputs to SI0 contain a Schmitt trigger circuit.

Whether or not to use SI0 and how to control it all can be

set by a program.

―

33~38

TEST0

~

TEST5

Test mode

control inputs

Test mode control input pins.

The test mode is selected when these pins are set high

and normal operation is selected when they are low.

These pins normally must be held low or left open (NC)

when used for this purpose. (Pulldown resistors are

built-in).

―

39~42

/HSO/OT19

SPCK/OT20

SPDA/OT21

COFS/OT22

CD control

signal outputs

/output ports

CD control output pins.

· /HSO : Playback speed mode output.

High = normal speed;

Low = double speed.

· SPCK : Processor status signal readout

clock output (176.4 kHz)

· SPDA : Processor status signal output.

· COFS : Correction system frame clock output

(7.35 kHz).

These pins can be switched for output ports by a program.

―

43 DOUT Digital output pin. ―

44 SBSY

CD control

input/outputs

Subcode block sync output pin. It outputs a high at the S1

position when subcode sync is detected.

―