TC9457F

2002-10-21

8

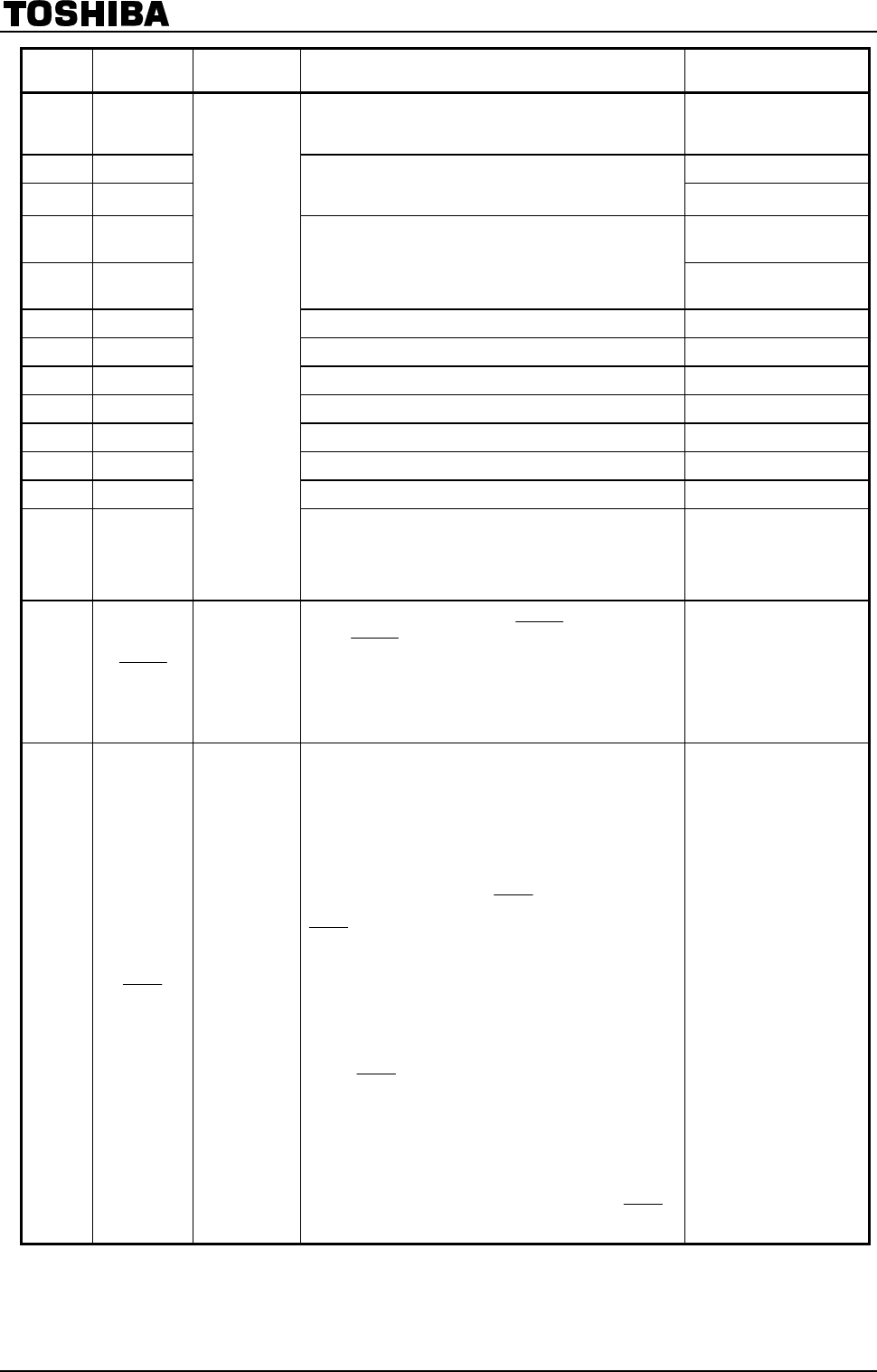

Pin No. Symbol Pin Name Function And Operation Remarks

74 SEL

APC circuit on/off signal output pin. When laser is on, this

pin goes to a high-impedance state when UHS = low and

outputs a high when UHS = high.

―

77 XV

SS

―

80 XV

DD

CD's crystal oscillator power supply pins. Normally,

connect these pins to the power supply lines that are used

in common for the V

DD

and V

SS

pins.

―

78 XI ―

79 XO

CD's crystal oscillator input/output pins. Normally, connect

16.9344 MHz here. This clock is used as the system clock

for the CD. After a system reset, it also is used as the

system clock on the controller side. Therefore, all of the

CD power supplies must be fed with power after a reset.

―

81 DVSR R-channel DA converter unit ground pin. ―

82 RO R-channel data forward output pin. ―

83 DVRR R-channel reference voltage pin. ―

84 DV

DD

DA converter unit power supply pin. ―

85 DVRL L-channel reference voltage pin. ―

86 LO L-channel data forward output pin. ―

87 DVSL L-channel DA converter unit ground pin. ―

88, 89 NC

CD control

input/outputs

NC pins. Normally, connect these pins to ground or leave

them open. Pin 89 serves dual purposes as the V

pp

pin of

an E

2

PROM product. Therefore, when this pin is left open,

it can be shared with an E

2

PROM product.

―

90 RESET Reset input

Device's system reset signal input pin.

The device remains reset while

RESET is held low and

when

RESET is released back high, the CD unit

becomes operational and the program starts from address

0. Normally, a system reset is asserted when a voltage of

2.7 V or more is applied to V

DD

when it is at 0 V

(power-on reset). Therefore, this pin must be pulled high

when used for this purpose.

―

91 HOLD

Hold mode

control input

This pin is used to input a signal that requests or clears

the hold mode.

Normally, use this pin for CD mode select signal input or

battery detection signal input.

There are two hold modes : clock stop mode (crystal

oscillator turned off) and a wait mode (CPU stopped).

These modes are entered by executing the CKSTP and

WAIT instructions, respectively.

The clock stop mode can be requested by a programmed

input: low level detection on

HOLD pin or forced

execution, and can be cleared by detecting a high on the

HOLD pin or a change of state in its input signal. When

the CKSTP instruction is executed, the clock generator

and the CPU stop operating and the device is placed in a

memory backup state. During this state, the device's

current consumption is reduced to 1µA or less. At the

same time, the display output and CMOS output ports are

automatically set low, and the Nch open-drain outputs are

turned off.

The wait mode is executed regardless of the input state

on the

HOLD pin, with the device's current consumption

reduced. In this mode, the user can choose to keep only

the crystal oscillator operating or have the CPU paused by

programming.

If the former is selected, all display outputs are set low

and other pins retain their state ; if the latter is selected, all

states are retained except that the CPU is temporarily

stopped.

This mode is cleared by a change of state in the

HOLD

input.

―