PLB PCI Full Bridge (v1.00a)

10 www.xilinx.com DS508 March 21, 2006

Product Specification

EARLY ACCESS

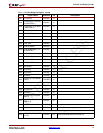

G27

IPIF BAR to which PCI

BAR 0

is mapped

C_PCIBAR2

IPIFBAR_0

Vector of length

C_PLB_AWIDTH

0x00000000

std_logic_

vector

G28

Power of 2 in the size in

bytes of PCI BAR 0

space

C_PCIBAR_

LEN_0

5 to 29 16 integer

G29

IPIF BAR to which PCI

BAR 1 is mapped

C_PCIBAR2IPI

FBAR_1

Vector of length

C_PLB_AWIDTH

0x00000000

std_logic_

vector

G30

Power of 2 in the size in

bytes of PCI BAR 1

space

C_PCIBAR_

LEN_1

5 to 29 16 integer

G31

IPIF BAR to which PCI

BAR 2 is mapped

C_PCIBAR2

IPIFBAR_2

Vector of length

C_PLB_AWIDTH

0x00000000

std_logic_

vector

G32

Power of 2 in the size in

bytes of PCI BAR 2

space

C_PCIBAR_

LEN_2

5 to 29 16 integer

G33 PCI address bus width

C_PCI_ABUS_

WIDTH

32 32 integer

G34 PCI data bus width

C_PCI_DBUS_

WIDTH

32 32 integer

G35

Both PCI2IPIF FIFO

address bus widths.

Usable depth is

2^C_PCI2IPIF_FIFO_A

BUS_WIDTH - 3

C_PCI2IPIF_

FIFO_ABUS_

WIDTH

4-14 9 integer

G36

Both IPIF2PCI FIFO

address bus widths.

Usable depth is

2^C_IPIF2PCI_FIFO_A

BUS_WIDTH - 3

C_IPIF2PCI_

FIFO_ABUS_

WIDTH

4-14 9 integer

G37

Include explicit

instantiation of INTR_A

io-buffer (must be 1 to

include io-buffer)

C_INCLUDE_

INTR_A_BUF

0 = not included

1 = included

1 integer

G38

Include explicit

instantiation of REQ_N

io-buffer (must be 1 to

include io-buffer)

C_INCLUDE_

REQ_N_BUF

0 = not included

1 = included

1 integer

G39

Minimum PCI2IPIF

FIFO occupancy level

that triggers the bridge

to initiate a prefetch PCI

read of a remote PCI

agent

C_TRIG_PCI_

READ_OCC_

LEVEL

5 to the lesser of 24 or

the PCI2IPIF FIFO

DEPTH-3. PCI2IPIF

FIFO DEPTH given by

2^C_PCI2IPIF_FIFO_

ABUS_WIDTH

32 integer

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic

Feature /

Description

Parameter

Name

Allowable Values

Default

Value

VHDL

Type