PLB PCI Full Bridge (v1.00a)

18 www.xilinx.com DS508 March 21, 2006

Product Specification

EARLY ACCESS

Port and Parameter Dependencies

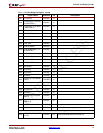

The dependencies between the IPI v3.0 Bridge design port (i.e., I/O signals) and parameters are shown

in

Table 1.

Table 3: PLB PCI Bridge Parameters-Port Dependencies

Generic Parameter Affects Depends Description

Bridge Features Parameter Group

G1 C_IPIFBAR_NUM G5-G25

The set of PLB/IPIF BAR-parameters of

N = 0 to C_IPIFBAR_NUM-1 are

meaningful. When C_IPIFBAR_NUM <

6, the parameters of N =

C_IPIFBAR_NUM up to and including 5

have no effect. If C_IPIFBAR_NUM = 6,

the set of PLB/IPIF BAR-parameters of N

= 0 to 5 are all meaningful (i.e., G2-G25

are meaningful).

G2 C_IPIFBAR_0 G3 G3

G2 to G3 define range in PLB-memory

space that is responded to by this device

(IPIF BAR)

G3 C_IPIFBAR_HIGHADDR_0 G2 G2

G2 to G3 define range in PLB-memory

space that is responded to by this device

(IPIF BAR)

G4 C_IPIFBAR2PCIBAR_0

G2, G3 and

G48

Meaningful only if G48 = 0 and in this

case only high-order bits that are the

same in G2 and G3 are meaningful.

G5 C_IPIF_SPACETYPE_0

G6 C_IPIFBAR_1 G7 G1 and G7

Meaningful only if G1>1, then G6 to G7

define the range in PLB-memory space

that is responded to by this device (IPIF

BAR)

G7 C_IPIFBAR_HIGHADDR_1 G6 G1 and G6

Meaningful only if G1>1, then G6 to G7

define the range in PLB-memory space

that is responded to by this device (IPIF

BAR)

G8 C_IPIFBAR2PCIBAR_1

G1, G6, G7

and G48

Meaningful only if G48 = 0 and G1>1. In

this case only high-order bits that are the

same in G6 and G7 are meaningful.

G9 C_IPIF_SPACETYPE_1 G1 Meaningful only if G1>1

G10 C_IPIFBAR_2 G11

G1 and

G11

Meaningful only if G1>2, then G10 to

G11 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)

G11 C_IPIFBAR_HIGHADDR_2 G10

G1 and

G10

Meaningful only if G1>2, then G10 to

G11 define the range in PLB-memory

space that is responded to by this device

(IPIF BAR)