PLB PCI Full Bridge (v1.00a)

DS508 March 21, 2006 www.xilinx.com 11

Product Specification

E

AR

L

Y

ACCESS

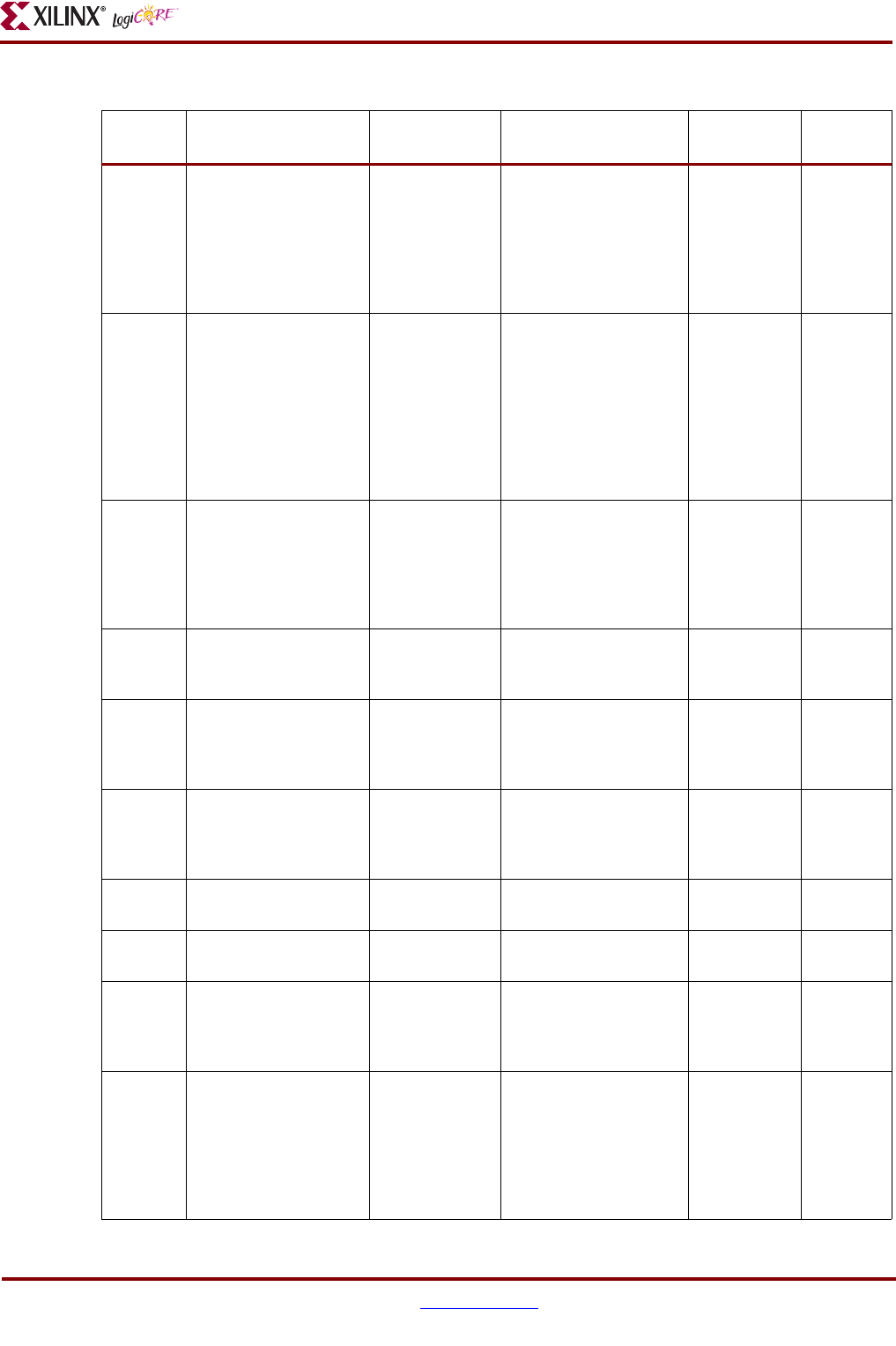

G40

PCI2IPIF FIFO

occupancy level in

double words that

triggers the bridge to

initiate an IPIF burst

write to remote PLB

device

C_TRIG_IPIF_

WRBURST_

OCC_LEVEL

2 to the lesser of 24 or

the PCI2IPIF FIFO

DEPTH-3. PCI2IPIF

FIFO DEPTH given by

2^C_PCI2IPIF_FIFO_A

BUS_WIDTH

8 integer

G41

IPIF2PCI FIFO

occupancy level that

starts data transfer

(Both as initiator and

target on PCI) to PCI

agent with multiple data

phases per transfer

(must meet 16 PCI

period maximum).

C_TRIG_PCI_

DATA_XFER_

OCC_LEVEL

2 to the lesser of 24 or

the IPIF2PCI FIFO

DEPTH-3. IPIF2PCI

FIFO DEPH given by

2^C_IPIF2PCI_FIFO_

ABUS_WIDTH

8 integer

G42

Minimum IPIF2PCI

FIFO occupancy level

that triggers bridge to

initiate a prefetch IPIF

read of a remote PLB

slave

C_TRIG_IPIF_

READ_OCC_

LEVEL

2 to the lesser of 24 or

the IPIF2PCI FIFO

DEPTH-3. IPIF2PCI

FIFO DEPH given by

2^C_IPIF2PCI_FIFO_

ABUS_WIDTH

16 integer

G43

Number of PCI retry

attempts in IPIF

posted-write operations

C_NUM_PCI_R

ETRIES_IN_

WRITES

Any integer 3 integer

G44

Number of PCI clock

periods between retries

in posted- write

operations

C_NUM_PCI_P

RDS_BETWN_

RETRIES_IN_

WRITES

Any integer 6 integer

G45

Number of IPIF retry

attempts in

posted-write PCI

initiator operations

C_NUM_IPIF_

RETRIES_IN_

WRITES

Any integer 6 integer

G46 Device base address

C_BASE

ADDR

Valid PLB address

(1), (2)

0xFFFFFFFF

std_logic_

vector

G47

Device absolute high

address

C_HIGHADDR Valid PLB address

(1), (2)

0x00000000

std_logic_

vector

G48

Include the registers for

high-order bits to be

substituted in

translation

C_INCLUDE_

BAROFFSET_

REG

1 = include

0 = exclude

0 integer

G49

Include the register for

local bridge device

number when

configuration

functionality

(C_INCLUDE_PCI_CO

NFIG =1) is included

C_INCLUDE_D

EVNUM_REG

1 = include

0 = exclude

0 integer

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic

Feature /

Description

Parameter

Name

Allowable Values

Default

Value

VHDL

Type