Read Datapath

R

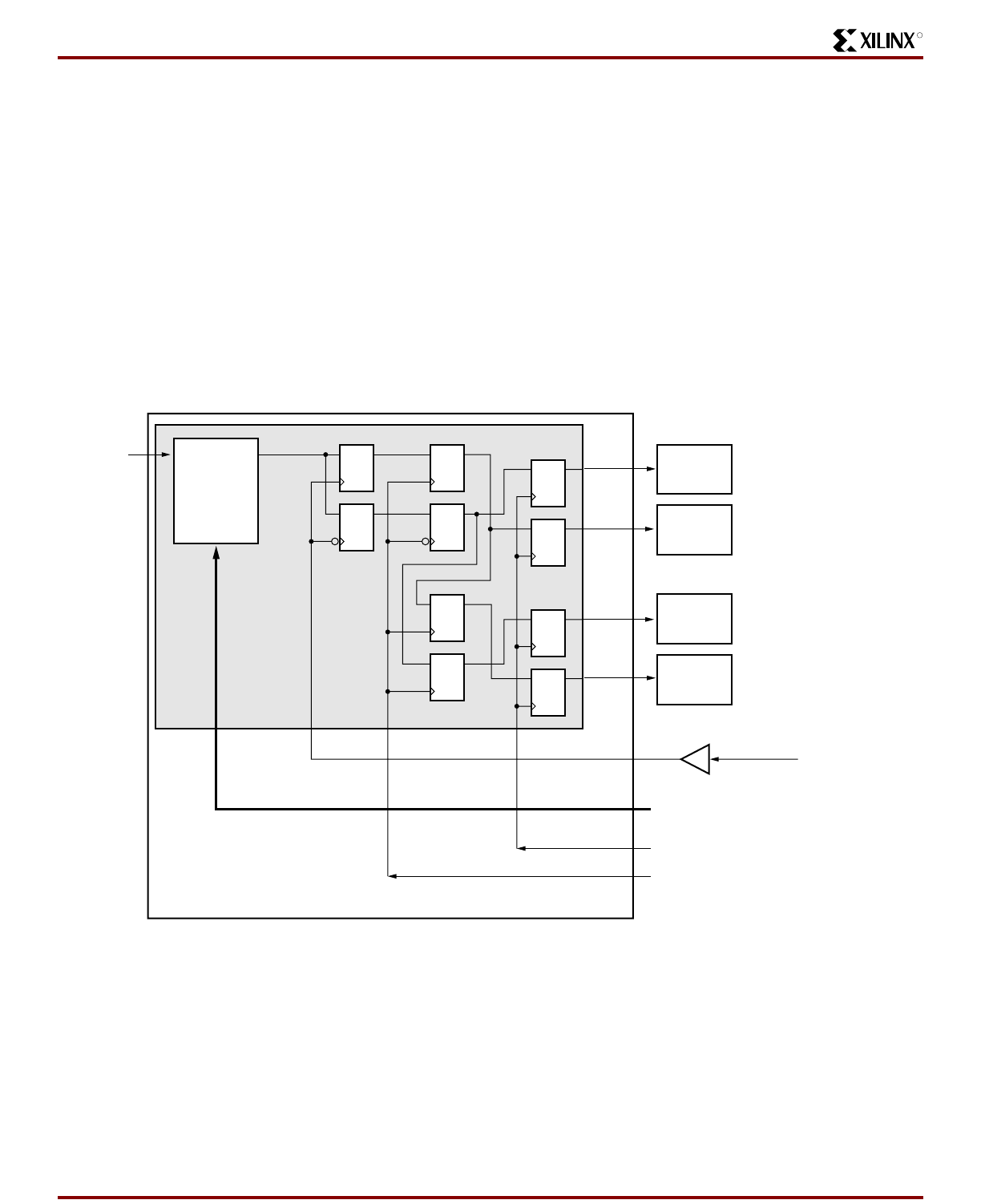

Read Datapath The read datapath comprises the read data capture and recapture stages. Both stages are

implemented in the built-in ISERDES available in every Virtex-4 I/O. The ISERDES has three

clock inputs: CLK, OCLK, and CLKDIV. The read data is captured in the CLK (DQS) domain,

recaptured in the OCLK (FPGA fast clock) domain, and finally transferred to the CLKDIV

(FPGA divided clock) domain to provide parallel data.

N CLK: The read DQS routed using BUFIO provides the CLK input of the ISERDES as

shown in Figure 7.

N OCLK: The OCLK input of ISERDES is connected to the CLK input of OSERDES in

hardware. In this design, the CLKfast_90 clock is provided to the ISERDES OCLK input

and the OSERDES CLK input. The clock phase used for OCLK is dictated by the phase

required for write data.

N CLKDIV: It is imperative for OCLK and CLKDIV clock inputs to be phase-aligned for

correct functionality. Therefore, the CLKDIV input is provided with CLKdiv_90 that is

phase-aligned to CLKfast_90.

Read Timing Analysis

To capture read data without errors in the ISERDES, read data and strobe must be delayed to

meet the setup and hold times of the flip-flops in the FPGA clock domain. Read data (DQ) and

strobe (DQS) are received edge-aligned at the FPGA. The differential DQS pair must be placed

on a clock-capable IO pair in order to access the BUFIO resource. The received read DQS is

then routed through the BUFIO resource to the CLK input of the ISERDES of the associated

data bits. The delay through the BUFIO and clock routing resources shifts the DQS to the right

with respect to data. The total delay through the BUFIO and clock resource is 595 ps in a -11

speed grade device and 555 ps in a -12 speed grade device.

Figure 7: Read Data Capture Using ISERDES

Q1

Q2

Q3

Q4

CLK OCLK CLKDIV

BUFIO

User Interface

FIFOs

DQS

IOB

ISERDES

Data Delay Value Determined

Using Training Pattern

CLKdiv_90

CLKfast_90

Read Data

Word 3

Read Data

Word 2

Read Data

Word 1

Read Data

Word 0

DQ

X721_07_063005

Delay

Read Data

to Align With

Strobe and

FPGA Clock

March 2006 Memory Interfaces Solution Guide 61