Read Datapath

R

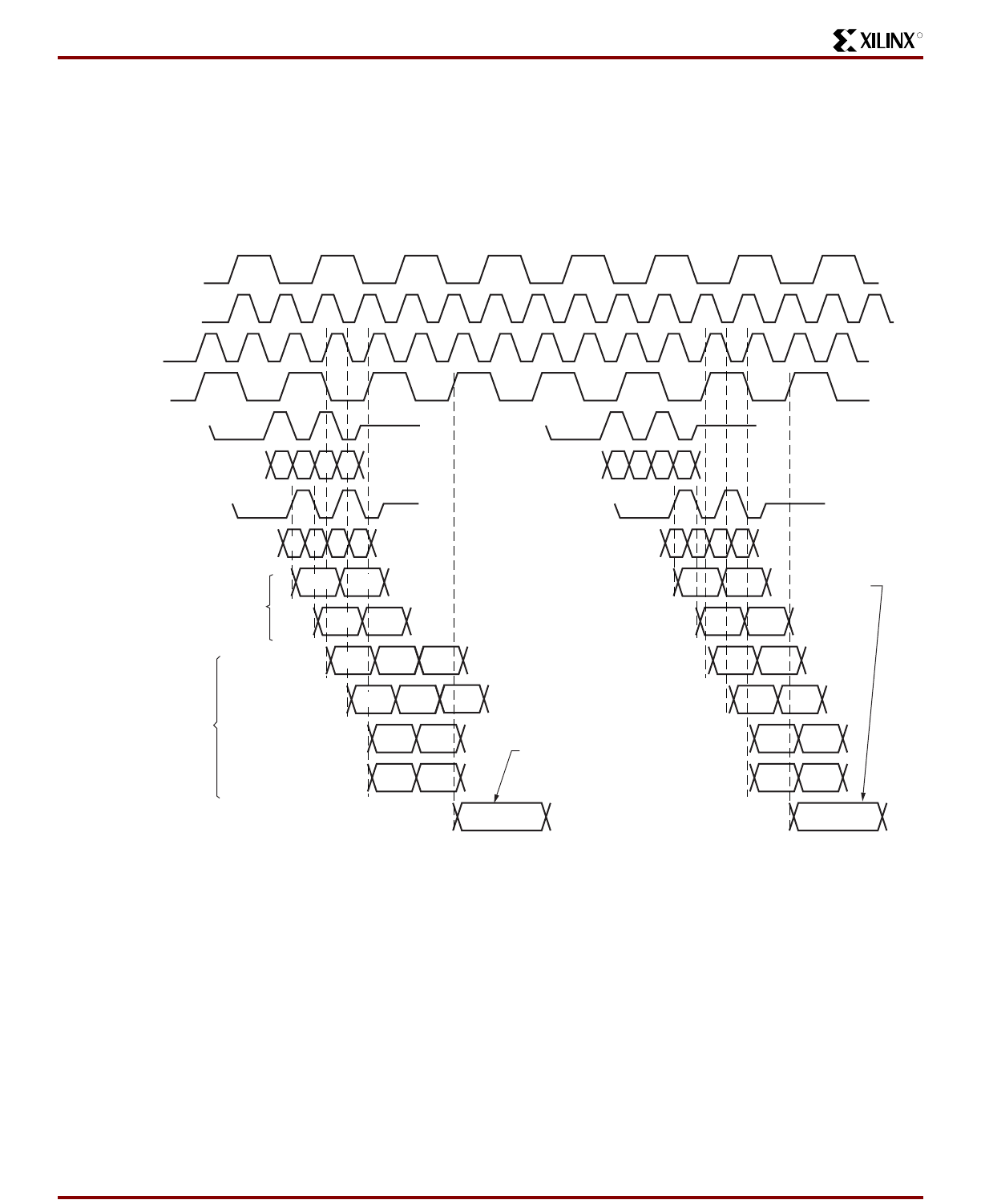

Figure 8 shows the timing waveform for read data and strobe delay determination. The

waveforms on the left show a case where the DQS is delayed due to BUFIO and clocking

resource, and the ISERDES outputs do not match the expected data pattern. The waveforms

on the right show a case where the DQS and DQ are delayed until the ISERDES outputs match

the expected data pattern. The lower end of the frequency range useful in this design is limited

by the number of available taps in the IDELAY block, the PCB trace delay, and the CAS latency

of the memory device.

Figure 8: Read Data and Strobe Delay

CLKdiv_0

CLKdiv_90

CLKfast_90

CLKfast_0

DQS @ FPGA

DQ @ FPGA

Parallel Data @ ISERDES

Outputs Q4, Q3, Q2, Q1

DQS @ ISERDES

delayed by BUFIO

and clocking resource

DQ

D0 D1 D2 D3

D0

D0

D1 D2

D2

D3

D1 D3

D0 D2

D1 D3

D0 D2

D1

D2,D3,D0,D1

D3

X721_08_112905

No Match

Incorrect Data

Sequence

DQS @ FPGA

DQ @ FPGA

Parallel Data @ ISERDES

Outputs Q4, Q3, Q2, Q1

DQS Delayed by Calibration

Delay @ ISERDES

DQ Delayed by Calibration Delay

D0 D1 D2 D3

D0

D0

D1 D2

D2

D3

D1 D3

D0 D2

D1 D3

D0 D2

D1

D0,D1,D2,D3

D3

Correct Data

Sequence

DQ Captured in DQS Domain

D0

D1

CLKfast_90

Domain

Input to Q2 Reg

Input to Q1 Reg

Input to Q3 Reg

Input to Q4 Reg

March 2006 Memory Interfaces Solution Guide 63