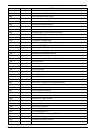

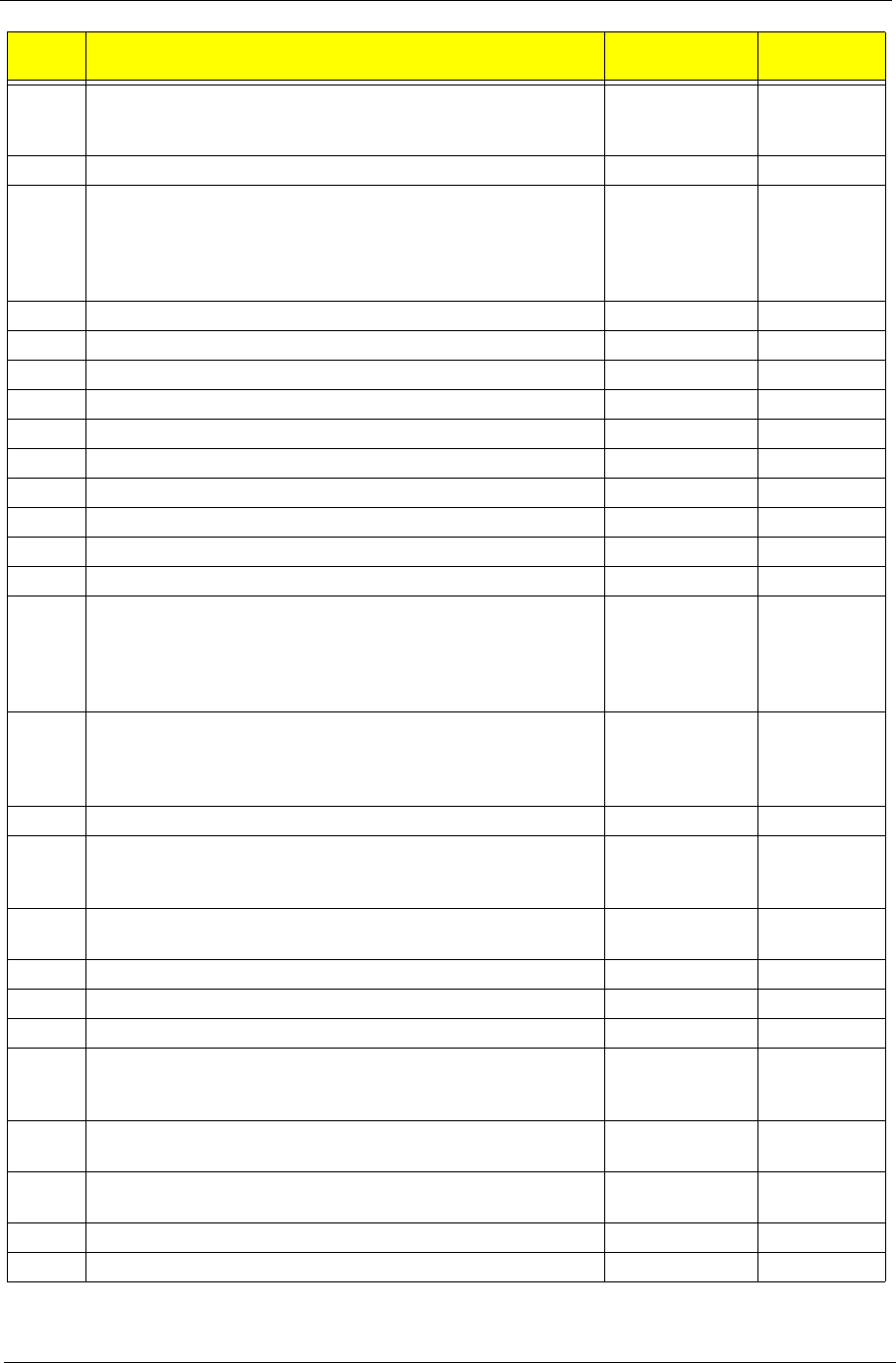

Chapter 4 141

0x7C Initialize the hardware interrupt vectors from 08 to 0F and from

70h to 77H. Also set the interrupt vectors from 60h to 66H to

zero.

LBT Core

0x41 ROM Pilot Init LBT Core

0x4B Initialize QuietBoot if it is installed. Enable both keyboard and

timer interrupts (IRQ0 and IRQ1). If your POST tasks require

interrupts off, preserve them with a PUSHF and CLI at the

beginning and a POPF at the end. If you change the PIC,

preserve the e

LBT Core

0xDE Initialize and UNDI ROM (fro remote flash) LBT Core

0xC6 Initial and install console for UCR LBT Core

0x4E Display copyright notice. LBT Core

0xD4 Get CPU branding string LBT Core

0x50 Display CPU type and speed LBT Core

0xC9 pretask before EISA init LBT Core

0x51 EISA Init LBT Core

0x5A Display prompt "Press F2 to enter SETUP" LBT Core

0x5B Disable CPU cache. LBT Core

0x5C Test RAM between 512K and 640K. LBT Core

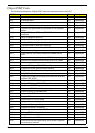

0x60 Determine and test the amount of extended memory available.

Determine if memory exists by writing to a few strategic

locations and see if the data can be read back. If so, perform

an address-line test and a RAM test on the memory. Save the

total extended

LBT Core

0x62 The amount of memory available. This test is dependent on the

processor, since the test will vary depending on the width of

memory (16 or 32 bits). This test will also use A20 as the skew

address to prevent corruption of the system memory.

LBT Core

0x64 Jump to UserPatch1. LBT Core

0x66 Set cache registers to their CMOS values if CMOS is valid,

unless auto configuration is enabled, in which case load cache

registers from the Setup default table.

LBT Core

0x68 Enable external cache and CPU cache if present. Configure

non-cacheable regions if necessary.

LBT Core

0x6A Display external cache size on the screen if it is non-zero. LBT Core

0x6C Display shadow message LBT Core

0xCA post EISA init LBT Core

0x70 Check flags in CMOS and in the TrustedCore data area for

errors detected during POST. Display error messages on the

screen.

LBT Core

0x72 Check status bits to see if configuration problems were

detected. If so, display error messages on the screen.

LBT Core

0x4F Initialize MultiBoot. Allocate memory for old and new MultiBoot

history tables.

LBT Core

0xCD Reclaim console vector after HW vectors initialized. LBT Core

0x7D Initialize Intelligent System Monitoring. LBT Core

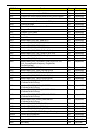

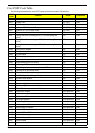

POST

Code

Function Phase Component