Schematic Diagrams

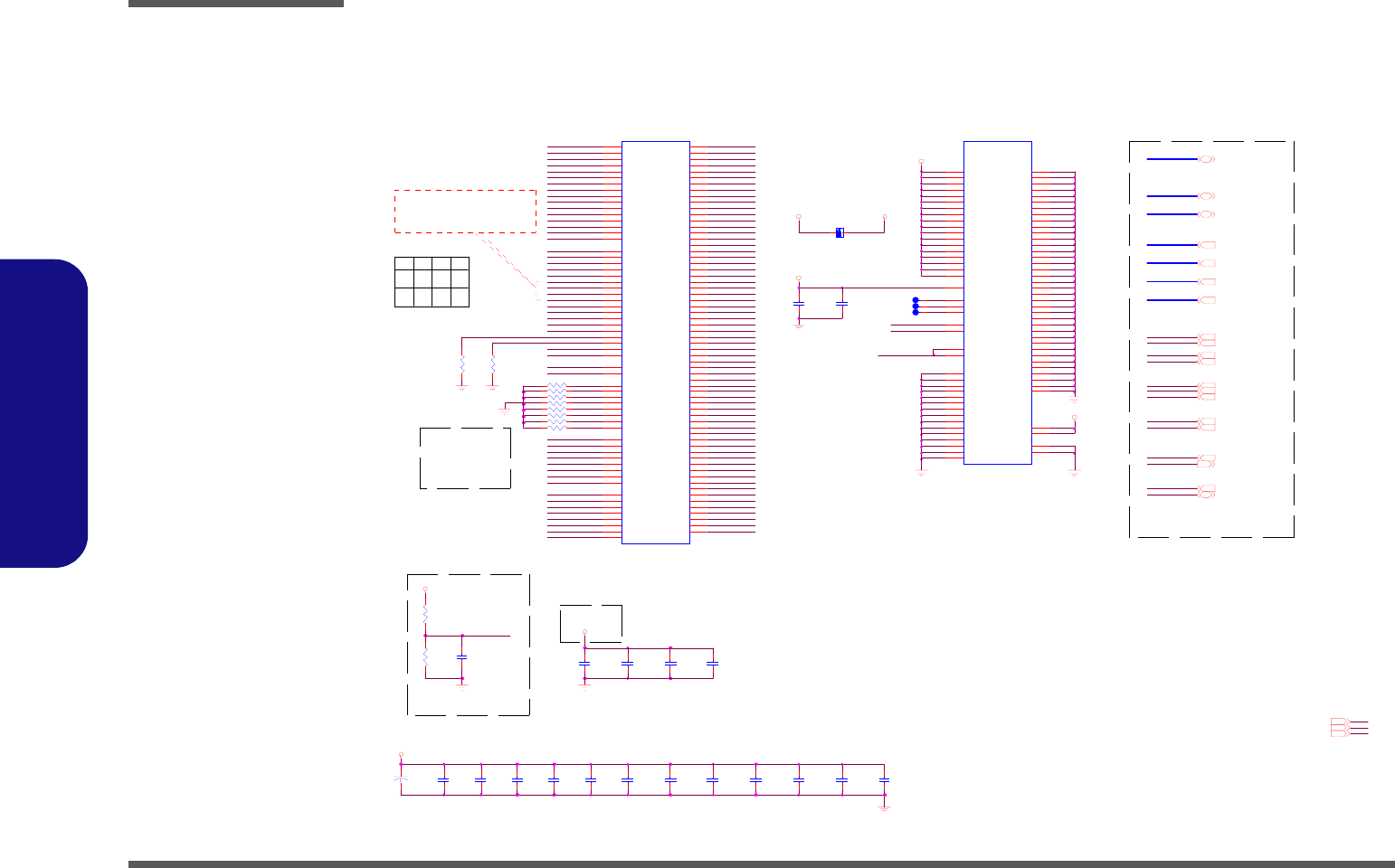

B - 8 DDR3 Channel A SO-DIMM_0

B.Schematic Diagrams

DDR3 Channel A SO-DIMM_0

VDDSPDA

VDDSPDA

1.5V

1.5V

3VS

0.75V

0.75 V

1.5V

1.5V4,5 , 8 ,9 , 40 ,4 3

3V S8,9,12,13,15..30,32,39,41,43

M_DATA_A[63:0] 2

M_MA A_A [15:0] 3

M_ DQS_ A_DP[ 7: 0] 2

M_ DQS_ A_DN [7 :0] 2

M_OD T_A[1: 0 ] 3

M_SBS_A[2:0] 3

M_SCKE _A [ 1 :0 ] 3

CK _M _CH0_0_DP 3

CK _M _CH0_0_DN 3

CK _M _CH0_1_DN 3

CK _M _CH0_1_DP 3

M_RA S_A _ N 3

M_CA S_A _ N 3

M_WE_A_ N 3

M_SCS_A_N0 3

M_SCS_A_N1 3

DDR 0_D RAMR ST 3

SCLK 8, 9,12,16 ,18,1 9,32

SDATA 8,9,12,16,18,19,32

PM_EXTTS_DDR# 8,9

0.75 V8,9,40

Z0703

CK_ M_C H0 _0_DP

M_W E _ A_N

SA0_DIM0

M_SCS_A_N1

M_CAS_A_N

M_DA TA_ A0

SDATA

M_ODT_A0

M_SCKE_A1

M_D QS_A _ D N0

M_ODT_A1

Z0701

M_MAA_A0

M_SCS_A_N0

CK_ M_C H0 _0_DN

M_SCKE_A0

M_SBS_A0

DD R0_DRAM RST

M_RAS_A_N

M_D QS_A _ D P0

Z0702

CK_ M_C H0 _1_DP

SA1_DIM0

CK_ M_C H0 _1_DN

PM_EXTTS_DDR#

SCLK

M _D AT A _A [63:0]

M_MAA_A[15:0]

M_DA TA_ A1

M_DA TA_ A2

M_DA TA_ A3

M_DA TA_ A4

M_DA TA_ A5

M_DA TA_ A6

M_DA TA_ A7

M_DA TA_ A8

M_DA TA_ A9

M_DA TA_ A10

M_DA TA_ A11

M_DA TA_ A12

M_DA TA_ A13

M_DA TA_ A14

M_DA TA_ A15

M_DA TA_ A16

M_DA TA_ A17

M_DA TA_ A18

M_DA TA_ A19

M_DA TA_ A20

M_DA TA_ A21

M_DA TA_ A22

M_DA TA_ A23

M_DA TA_ A24

M_DA TA_ A25

M_DA TA_ A26

M_DA TA_ A27

M_DA TA_ A28

M_DA TA_ A29

M_DA TA_ A30

M_DA TA_ A31

M_DA TA_ A32

M_DA TA_ A33

M_DA TA_ A34

M_DA TA_ A35

M_DA TA_ A36

M_DA TA_ A37

M_DA TA_ A38

M_DA TA_ A39

M_DA TA_ A40

M_DA TA_ A41

M_DA TA_ A42

M_DA TA_ A43

M_DA TA_ A44

M_DA TA_ A45

M_DA TA_ A46

M_DA TA_ A47

M_DA TA_ A48

M_DA TA_ A49

M_DA TA_ A50

M_DA TA_ A51

M_DA TA_ A52

M_DA TA_ A53

M_DA TA_ A54

M_DA TA_ A55

M_DA TA_ A56

M_DA TA_ A57

M_DA TA_ A58

M_DA TA_ A59

M_DA TA_ A60

M_DA TA_ A61

M_DA TA_ A62

M_DA TA_ A63

M_DQS_A_DP[7:0]

M_D QS_A _ D P1

M_D QS_A _ D P2

M_D QS_A _ D P3

M_D QS_A _ D P4

M_D QS_A _ D P5

M_D QS_A _ D P6

M_D QS_A _ D P7

M_DQS_A_DN[7:0]

M_D QS_A _ D N1

M_D QS_A _ D N2

M_D QS_A _ D N3

M_D QS_A _ D N4

M_D QS_A _ D N5

M_D QS_A _ D N6

M_D QS_A _ D N7

M_ODT_A[1:0]

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_SBS_A1

M_SBS_A2 M_SBS_A[2:0]

M_SCKE_A[1:0]

CK _M_ CH 0 _0_DP

CK _M_ CH 0 _0_DN

CK _M_ CH 0 _1_DP

CK _M_ CH 0 _1_DN

M_RAS_A_N

M_CAS_A_N

M_WE_A_N

M_SCS_A_N0

M_SCS_A_N1

D DR0 _D RAMR ST

SCLK

SDATA

PM_EXTTS_D DR#

DIMM_CA_VREF_A

DIMM_CA_VREF_A

M_MAA_A15

Z0704

Z0705

Z0706

Z0707

Z0708

Z0709

Z0710

Z0711

+

C475

100U_6.3V_B

JD IMM1A

DD R3_ SODI MM0_2 04P

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

12 9

13 1

14 1

14 3

13 0

13 2

14 0

14 2

14 7

14 9

15 7

15 9

14 6

14 8

15 8

16 0

16 3

16 5

17 5

17 7

16 4

16 6

17 4

17 6

18 1

18 3

19 1

19 3

18 0

18 2

19 2

19 4

109

108

110

113

115

114

121

73

74

101

103

102

104

200

202

201

197

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

116

120

79

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

BA0

BA1

RAS#

WE#

CAS#

S0#

S1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

SDA

SCL

SA1

SA0

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

ODT0

ODT1

BA2

C1 06

.1U_10V_X7R_04

C1 05

4.7U_ 6.3V_0 6

R42

1K_1%_04

C91

.1U_10V_X7R_04

C44 9

2.2U_16V_X5R_06

C73

10 U_1 0V _ 08

C448

.1 U_10V_ X7R _04

C4 68

.1U_10V_X7R_04

C452

.1U _10 V _X7 R_04

C7 5

.01U_16V_X7R_04

C77

.1 U_ 10V_ X7R _0 4

C84

4.7U_6.3V_06

C470

10U_10V_08

C54

.1 U_1 0V_X7R_04

R43 0_04

JDIMM1B

DDR3_SODIMM0_204P

75

76

81

82

87

88

93

94

99

100

105

106

199

77

122

125

1

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

GND2

GND1

204

203

126

30

198

111

112

118

117

123

124

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD1 0

VDD1 1

VDD1 2

VDDSPD

NC 1

NC 2

NC TEST

VREF_DQ

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

G2

G1

VTT2

VTT1

VREF_CA

RESET#

EVEN T#

VDD1 3

VDD1 4

VDD1 6

VDD1 5

VDD1 7

VDD1 8

C88

1U_6.3V_04

C8 6

10 U _ 10 V_08

C467

.1 U_10V_X7R_04

R45

10 K _04

R41

1K_1%_04

C71

10U_10V_08

R50 0_04

C4 71

1 0U _ 10V_08

C472

*1 0u_10 V _08

R48 0_04

NC3

NC_ 04

R46

10 K _04

R49 0_04

R51 0_04

R44 0_04

R52 0_04

R47 0_04

MS:8.5 / 5 / 8.5

SL: 4 / 4 / 4

Layout Note:

CLK0/space/CLK_1

SO-DIMM0

ChannelA

X58 ? ? ? ?

???ECC??,

?? DM ?????OK

From power 0.75V

CLOSE TO SO-DIMM_0

15mils trace

34mils spacing

ChannelA

M_DQS_A_DP8

M_DQS_A_DN8

20mils traceLow

Low

Low

LowHigh

HighSA0

SA1

DIM0 CHA CHB CHC

M_CB_ECC_A[7:0]

Sheet 7 of 47

DDR3 Channel A

SO-DIMM_0