CY7C68300C/CY7C68301C

CY7C68320C/CY7C68321C

Document 001-05809 Rev. *A Page 14 of 42

interface and the attached mass storage device, especially if

Ultra DMA Mode is used.

VBUS_ATA_ENABLE

VBUS_ATA_ENABLE is typically used to indicate to the

AT2LP that power is present on VBUS. This pin is polled by

the AT2LP at startup and then every 20 ms thereafter. If this

pin is ‘0’, the AT2LP releases the pull up on D+ as required by

the USB specification.

Also, if bit 4 of configuration address 0x08 is ‘1’, the ATA

interface pins are placed in a Hi-Z state when

VBUS_ATA_ENABLE is ‘0’. If bit 4 of configuration address

0x08 is ‘0’, the ATA interface pins are still driven when

VBUS_ATA_ENABLE is ‘0’.

ATAPUEN

This output can be used to control the required host pull up

resistors on the ATA interface in a bus-powered design to

minimize unnecessary power consumption when the AT2LP is

in suspend. ATAPUEN is driven to ‘0’ when the ATA bus is

inactive. ATAPUEN is driven to ‘1’ when the ATA bus is active.

ATAPUEN is set to a Hi-Z state along with all other ATA

interface pins if VBUS_ATA_ENABLE is deasserted and the

ATA_EN functionality (bit 4 of configuration address 0x08) is

enabled (0).

ATAPUEN can also be configured as a GPIO input. See “HID

Functions for Button Controls” on page 15 for more infor-

mation on HID functionality.

PWR500#

The AT2LP asserts PWR500# to indicate that VBUS current

may be drawn up to the limit specified by the bMaxPower field

of the USB configuration descriptors. If the AT2LP enters a

low-power state, PWR500# is deasserted. When normal

operation is resumed, PWR500# is restored. The PWR500#

pin must never be used to control power sources for the

AT2LP. In the 56-pin package, PWR500# only functions during

bus-powered operation.

PWR500# can also be configured as a GPIO input. See “HID

Functions for Button Controls” on page 15 for more infor-

mation on HID functionality.

VBUSPWRD

VBUSPWRD is used to indicate self- or bus-powered

operation. Some designs require the ability to operate in either

self- or bus-powered modes. The VBUSPWRD input pin

enables these devices to switch between self-powered and

bus-powered modes by changing the contents of the

bMaxPower field and the self-powered bit in the reported

configuration descriptors (see Table 4).

Note that current USB host drivers do not poll the device for

this information, so the effect of this pin is only seen on a USB

or power on reset.

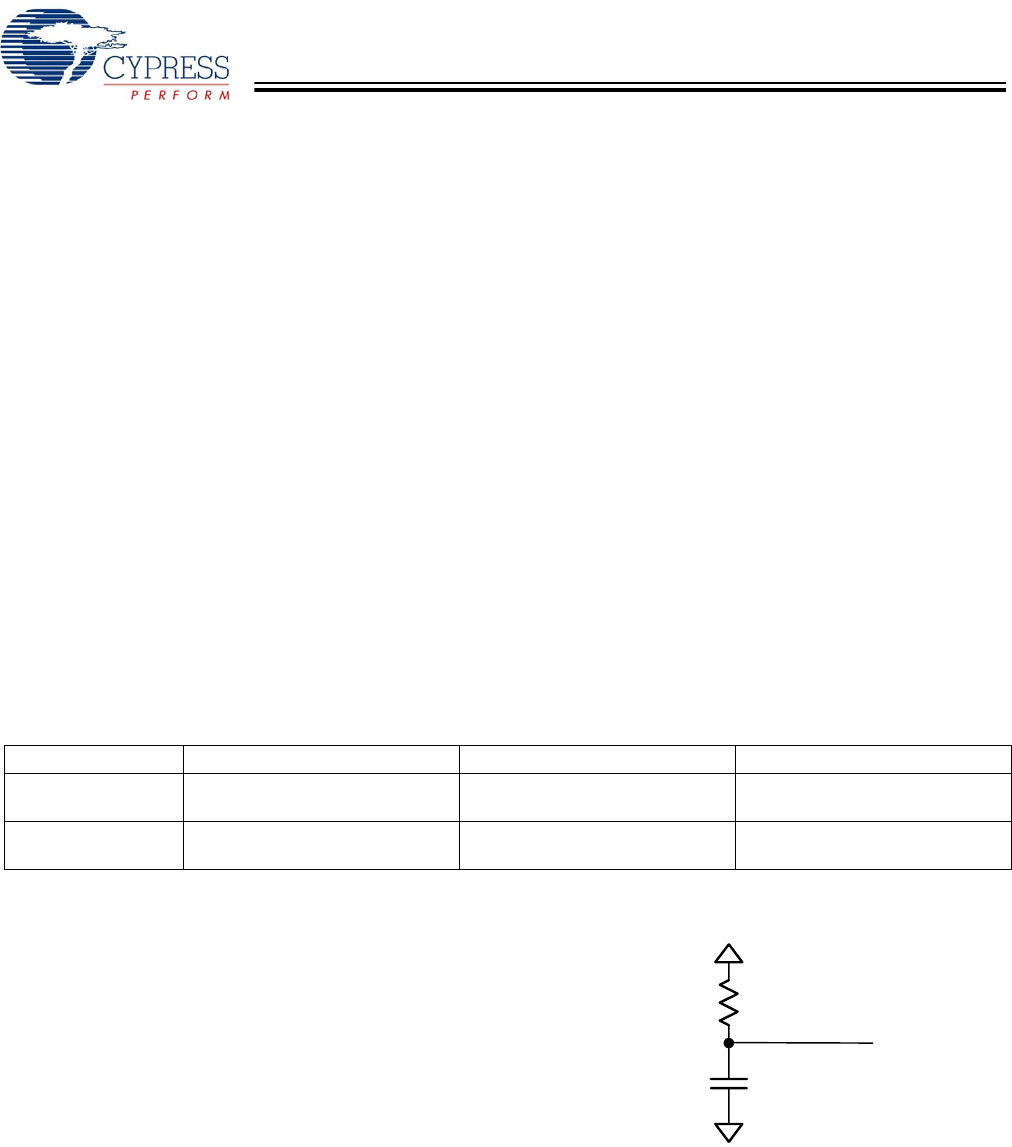

RESET#

Asserting RESET# for 10 ms resets the entire AT2LP. In

self-powered designs, this pin is normally tied to V

CC

through

a 100k resistor, and to GND through a 0.1 μF capacitor, as

shown in Figure 9.

Cypress does not recommend an RC reset circuit for

bus-powered devices because of the potential for VBUS

voltage drop, which may result in a startup time that exceeds

the USB limit. Refer to the application note titled EZ-USB

FX2™/AT2™/SX2™ Reset and Power Considerations, at

www.cypress.com, for more information.

While the AT2LP is in reset, all pins are held at their default

startup state.

Table 4. Behavior of Descriptor Data that is Dependent Upon VBUSPWRD State

Pin VBUSPWRD = ‘1’ VBUSPWRD = ‘0’ VBUSPWRD N/A (56-pin)

bMaxPower

Reported Value

0xFA

(500 mA)

0x01

(2 mA)

The value from configuration

address 0x34 is used.

bmAttributes bit 6

Reported Value

‘0’

(bus-powered)

‘1’

(self-powered)

‘0’ if bMaxPower > 0x01

‘1’ if bMaxPower ≤ 0x01

Figure 9. R/C Reset Circuit for Self-powered Designs

100KΩ

0.1μF

RESET#

[+] Feedback