CY7C68300C/CY7C68301C

CY7C68320C/CY7C68321C

Document 001-05809 Rev. *A Page 3 of 42

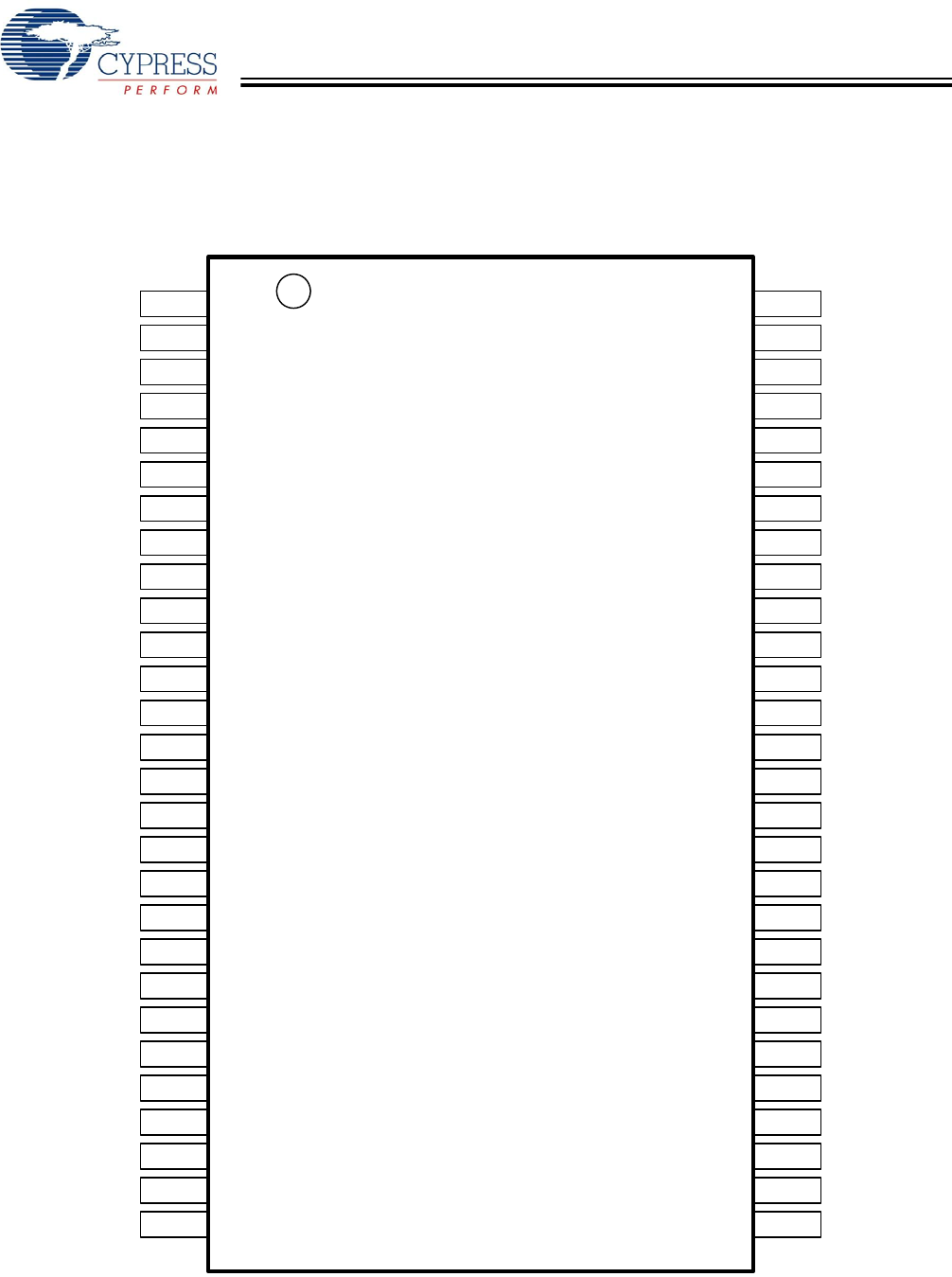

Pin Diagrams

The AT2LP is available in different package types to meet a variety of design needs. The CY7C68320C/321C is available in 56-pin

QFN and 100-pin TQFP packages to provide the greatest flexibility for new designs. The CY7C68300C/301C is available in 56-pin

SSOP and QFN package types to ensure backward compatibility with CY7C68300A designs.

Figure 2. 56-pin SSOP Pinout (CY7C68300C/CY7C68301C only)

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

1

2

3

4

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

56

55

54

53

ATAPUEN (GND)

VCC

GND

IORDY

DMARQ

AVCC

XTALOUT

XTALIN

AGND

VCC

DPLUS

DMINUS

GND

VCC

GND

PWR500# (PU 10K)

GND (Reserved)

SCL

SDA

VCC

DD0

DD1

DD2

DD3

DD13

DD14

DD15

GND

EZ-USB AT2LP

CY7C68300C

CY7C68301C

56-pin SSOP

DD8

(ATA_EN) VBUS_ATA_ENABLE

VCC

RESET#

GND

ARESET#

(VBUS_PWR_VALID) DA2

CS1#

CS0#

(DA2) DRVPWRVLD

DA1

DA0

INTRQ

VCC

DMACK#

DIOR#

DIOW#

GND

VCC

GND

DD7

DD6

DD5

DD4

DD12

DD11

DD10

DD9

NOTE: Labels in italics denote pin functionality

during CY7C68300A compatibility mode.

[+] Feedback