SL811HS

Document 38-08008 Rev. *D Page 29 of 32

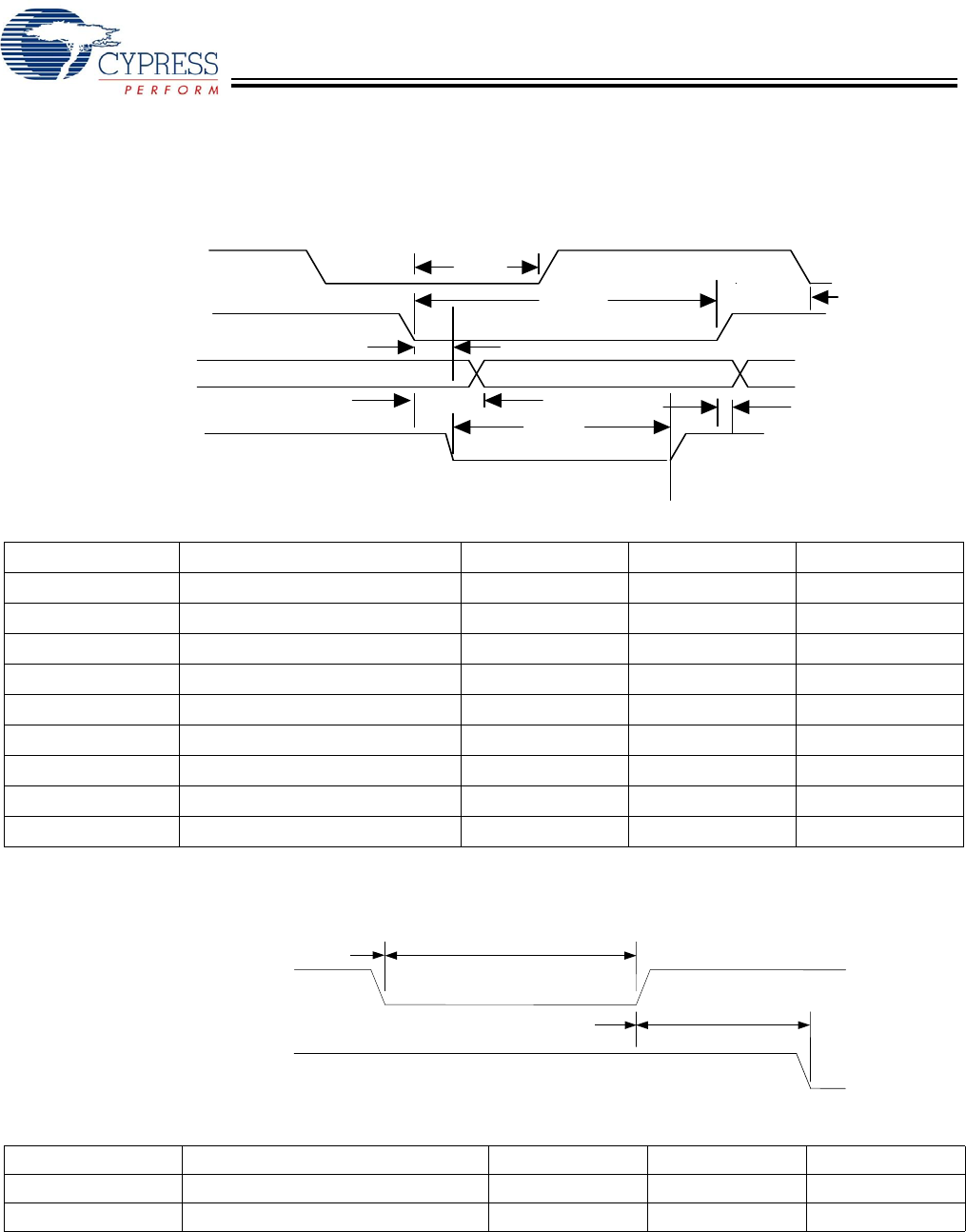

DMA Read Cycle

Note Data is held until nDACK goes high regardless of state of nREAD.

Reset Timing

Note Clock is 48 MHz nominal.

Parameter Description Min. Typ. Max.

tdack nDACK low 100 ns

tddrdlo nDACK to nRD low delay 0 ns

tdckdr nDACK low to nDRQ high delay 5 ns

tdrdp nRD pulse width 90 ns

tdhld Date hold after nDACK high 5 ns

tddaccs Data access from nDACK low 85 ns

tdrdack nRD high to nDACK high 0 ns

tdakrq nDRQ low after nDACK high 5 ns

trdcycle DMA Read Cycle Time 150 ns

nDRQ

nDACK

D0-D7

DATA

nRD

SL811 DMA READ CYCLE TIMING

tdrdp

tdaccs

tdack

tdhld

tddrdlo

tdckdr

tdakrq

SL811 DMA Read Cycle Timing

nRST

treset

nRD or nWR

tioact

Reset Timing

Parameter Description Min. Typ. Max.

t

RESET

nRst Pulse width 16 clocks

t

IOACT

nRst HIGH to nRD or nWR active 16 clocks