Dell™ PowerEdge™ R710 Technical Guidebook

24

•OnechannelperCPUpopulated:

•ThisisasimpleMemoryOptimizedmode.Mirroringisnotsupported.

The PowerEdge R710 memory interface supports memory demand and patrol scrubbing, single-bit

correction and multi-bit error detection. Correction of a x4 or x8 device failure is also possible with

SDDC in the Advanced ECC mode. Additionally, correction of a x4 device failure is possible in the Memory

Optimized mode. If DIMMs of dierent speeds are mixed, all channels will operate at the fastest common

frequency. RDIMMs and UDIMMs cannot be mixed.

•Ifmemorymirroringisenabled,identicalDIMMsmustbeinstalledinthesameslotsacrossboth

channels.

•Thethirdchannelofeachprocessorisunavailableformemorymirroring.

•TherstDIMMslotineachchanneliscolor-codedwithwhiteejectiontabsforeaseof

installation.

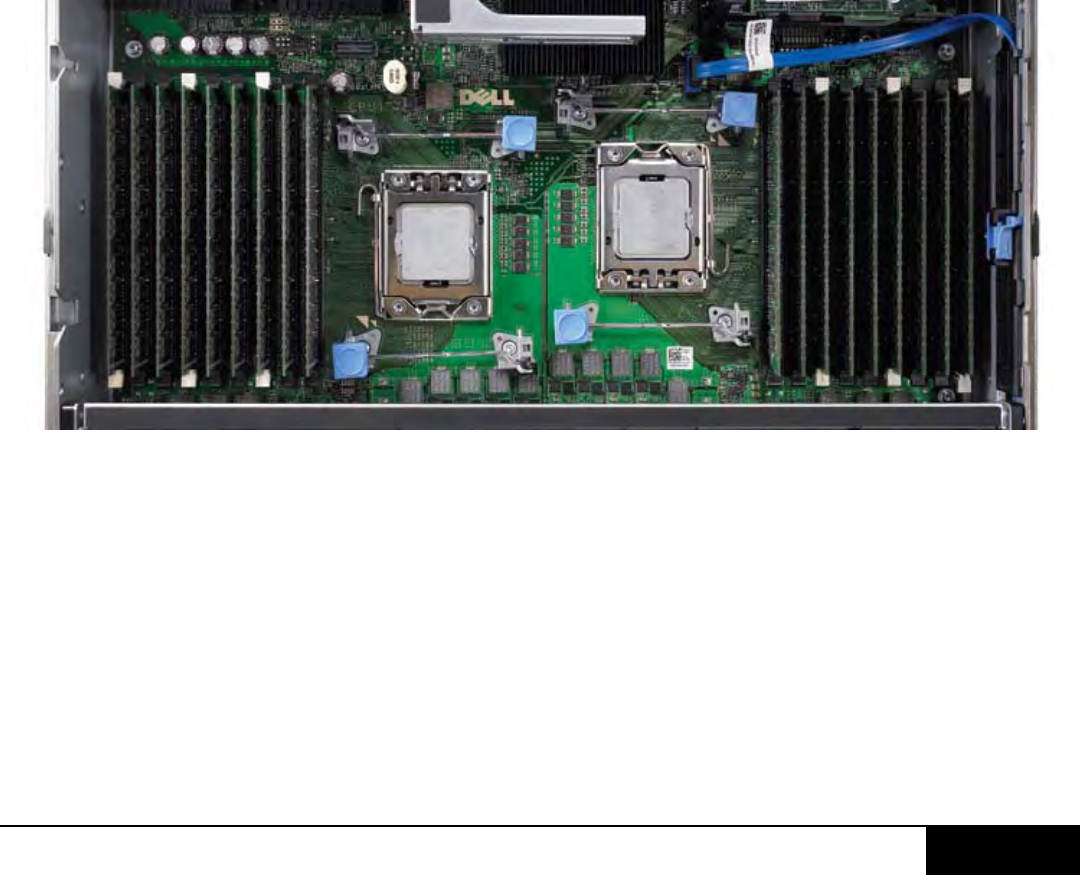

•TheDIMMsocketsareplaced450mils(11.43mm)apart,center-to-centerinordertoprovide

enough space for sucient airflow to cool stacked DIMMs.

•ThePER710memorysystemsupportsupto18DIMMs.DIMMsmustbeinstalledineachchannel

starting with the DIMM farthest from the processor. Population order will be identified by the

silkscreen designator and the System Information Label (SIL) located on the chassis cover.

•MemoryOptimized:{1,2,3},{4,5,6},{7,8,9}

•AdvancedECCorMirrored:{2,3},{5,6},{8,9}

•QuadRankorUDIMM:{1,2,3},{4,5,6},{7,8,9}

C. Speed

Memory Speed Limitations

The memory frequency is determined by a variety of inputs:

•SpeedoftheDIMMs

•SpeedsupportedbytheCPU

•CongurationoftheDIMMs