7.6 Bus Phases

C156-E228-02EN 7-19

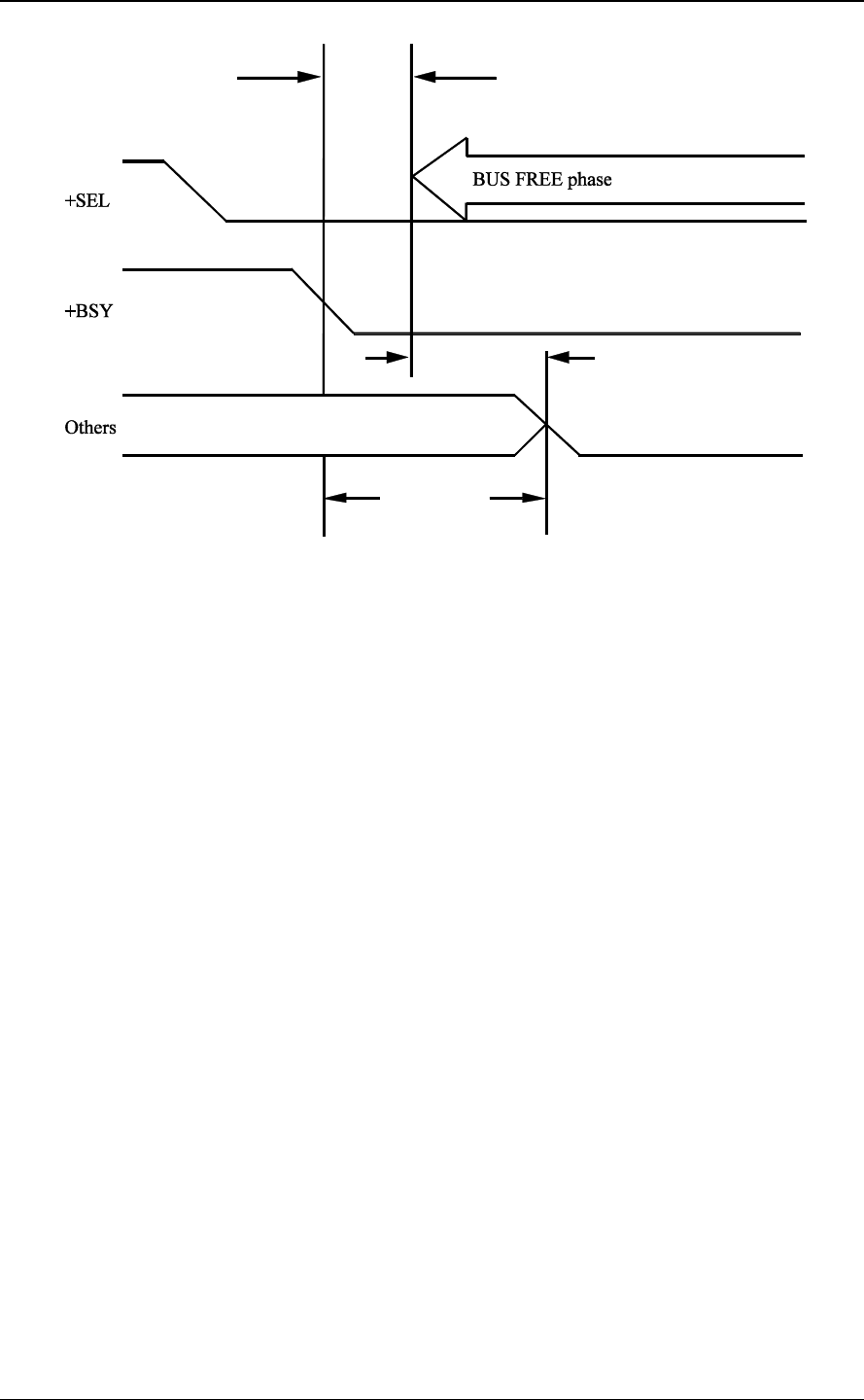

Bus Clear Delay (Max)

B

us Settle Delay +

Bus Clear Delay (Max)

Bus Settle Delay (Min)

Figure 7.9 BUS FREE phase

Transition to a BUS FREE phase occurs when the TARG stops the BSY signal in

one of the following events:

• When the RESET condition has been detected

• When the TARG has received ABORT message

• When the TARG has received a BUS DEVICE RESET message

• When the TARG has sent a DISCONNECT message normally

• When the TARG has sent a COMMAND COMPLETE message normally

If a SELECTION or RESELECTION phase is terminated unsuccessfully, the

SCSI bus enters a BUS FREE phase. This BUS FREE phase is generated when

the SEL signal becomes false.

In cases other than the above, if the TARG negates the BSY signal to enter a BUS

FREE phase, the TARG informs the INIT that it has detected an ERROR

condition on the SCSI bus. The TARG can enter a BUS FREE phase forcibly

regardless of the ATN signal status; the INIT must treat that phase transition as

indicating abnormal end of a command. The TARG clears all retained data or

status and terminates the command being executed. It can then create sense data

indicating the detailed error condition. If the INIT detects a BUS FREE phase

when it is not expected, it should issue a REQUEST SENSE command to read the

sense data.