54

2 System Board - (SiS Chipset) (Part Number: D4051-63001)

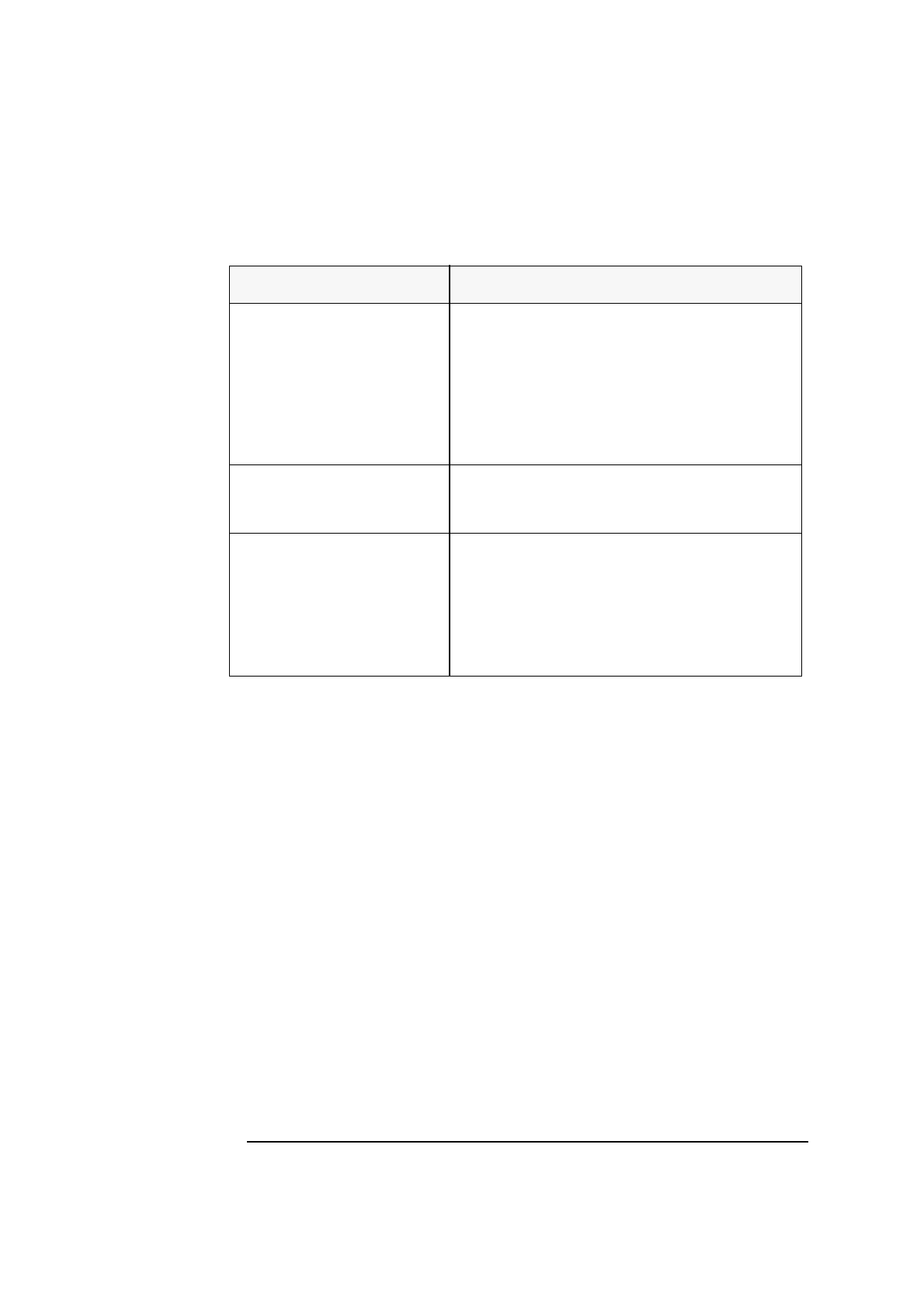

Devices on the ISA Bus

Serial/Parallel Ports

The Super I/O chip supports two serial ports and one bidirectional parallel

port. The serial ports are high speed UARTs with 16-Byte FIFOs, and can be

programmed as COM1, COM2, COM3, COM4, or disabled.

The parallel port can operate in four modes:

• Standard mode (PC/XT, PC/AT, and PS/2 compatible)

• Bidirectional mode (PC/XT, PC/AT, and PS/2 compatible)

• Enhanced mode (Enhanced Parallel Port or EPP compatible)

• High speed mode (MS/HP Extended Capabilities Port or ECP

compatible).

It can be programmed as LPT1 (378h, IRQ7), LPT2 (278h, IRQ5), or

disabled.

16 Single-Bit General Purpose I/O ports

(GPIO)

❒ Modifiable addresses that are referenced by a 16-bit program-

mable register.

❒ Programmable direction for each signal (input or output).

❒ Programmable drive type for each output pin (open-drain or

push-pull).

❒ Programmable option for internal pull-up resistor on each input

pin.

❒ A back-drive protection circuit.

Clock source options ❒ Source is a 32.768 kHz crystal (an internal frequency multiplier

generates all the required internal frequencies).

❒ Source may be either a 48 MHz or 24 MHz clock input signal.

General features ❒ All accesses to the Super I/O chip activates a Zero Wait State

(ZWS) signal, except for accesses to the Enhanced Parallel Port

(EPP) and to configuration registers.

❒ Accesses to all configuration registers is through an Index and a

Data register, which can be relocated within the ISA I/O address

space.

❒ 160-pin Plastic Quad Flatpack (PQFP) package.

Function Features