72

3 System Board (P/Ns D3657-63001 and D3661-63001)

Devices on the Processor Local Bus

Individual pages of memory can be configured as cacheable or non-

cacheable by software or hardware. They can also be enabled and disabled

by hardware or software.

Data Integrity

The processor uses a number of techniques to maintain data integrity. It

employs two methods of error detection:

• Data Parity Checking

This is supported on a byte-by-byte basis, generating parity bits for data

addresses sent out of the microprocessor. These parity bits are not used

by the external subsystems.

• Internally

The processor uses functional redundancy checking to provide maximum

error detection of the processor and its interface.

Bus Frequencies

The Pentium processor uses internal clock multiplication. For example, a

150 MHz processor multiplies the 60 MHz system clock by 2.5.

Switches 1 and 2 set the frequency of the Processor-Local bus.

Switches 3 and 4 set the clock multiplier ratio (system clock : local bus).

Switch 7 sets the ISA bus speed.

If a processor upgrade is installed, the switch settings may need to be

changed to adapt to the new processor. The following table shows the

settings required for the different processors.

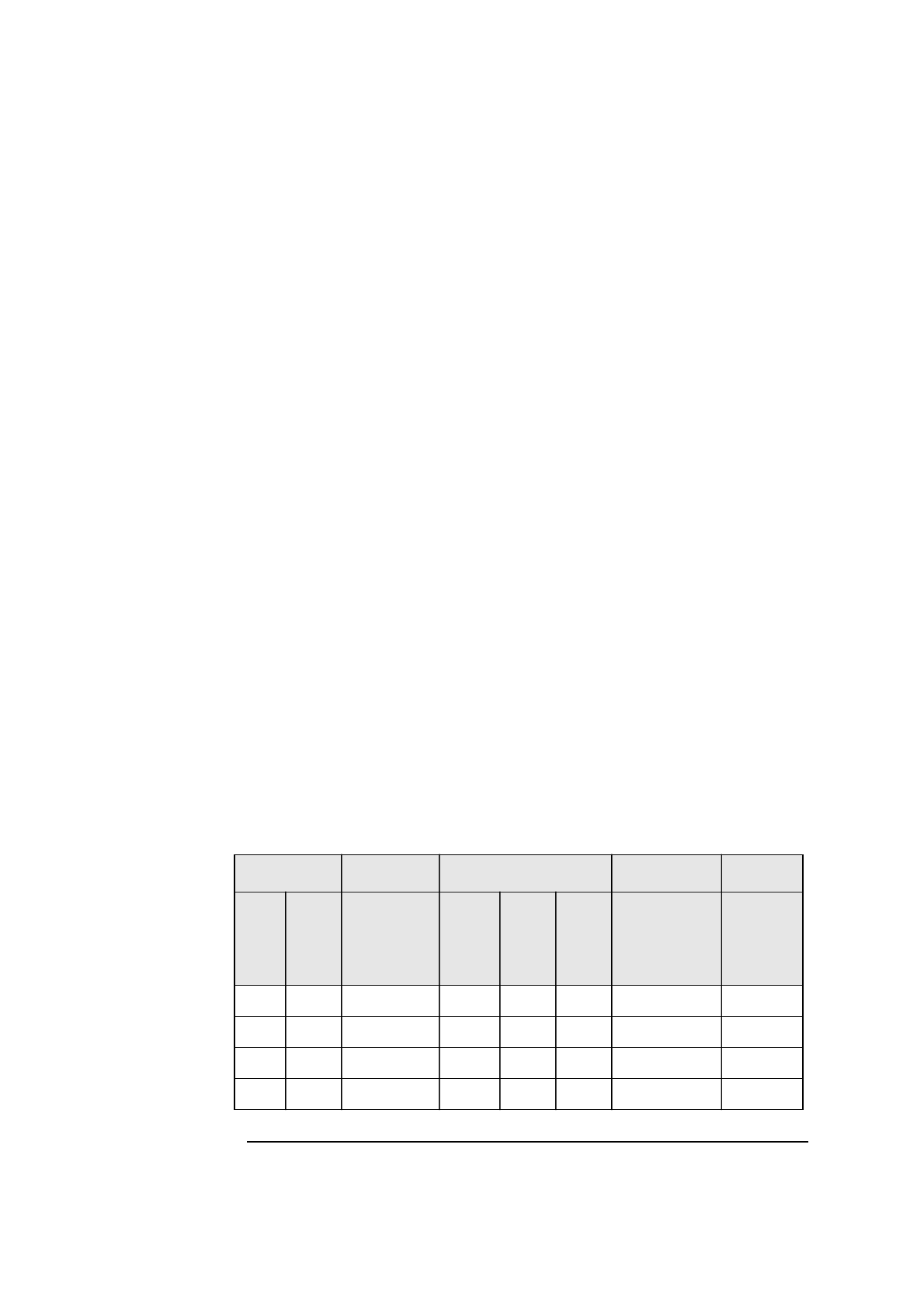

Switch Switch

1 2

Processor-

Local Bus

Frequency

3 4 7

Frequency

Ratio

(Processor:

Local Bus)

Processor

Frequency

Open Closed 66 MHz Open Open Closed 1.5 100 MHz

Closed Open 60 MHz Closed Open Closed 2 120 MHz

Open Closed 66 MHz Closed Open Closed 2 133 MHz

Closed Open 60 MHz Closed Closed Closed 2.5 150 MHz