53

4 BIOS Overview

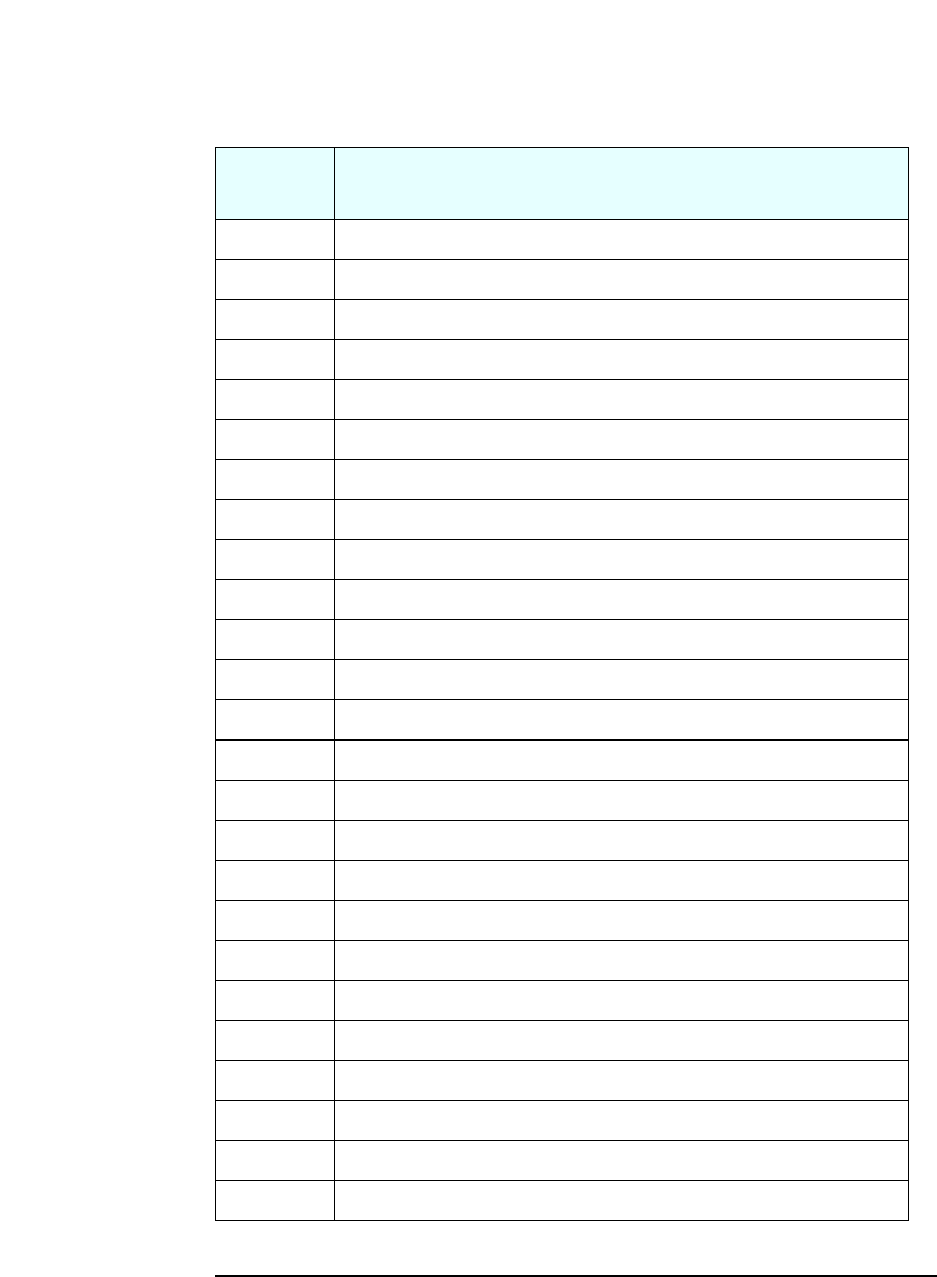

Order in Which the POST Tests are Performed

67h Initialize Multi Processor APIC

68h Enable external and CPU caches

69h Setup System Management Mode (SMM) area

6Ah Display external L2 cache size

6Ch Display shadow-area message

6Eh Display possible high address for UMB recovery

70h Display error messages

72h Check for configuration errors

74h Test real-time clock

76h Check for keyboard errors

7Ah Test for key lock on

7Ch Set up hardware interrupt vectors

7Eh Initialize coprocessor if present

80h Disable onboard Super I/O ports and IRQs

81h Late POST device initialization

82h Detect and install external RS 232 ports

83h Configure non-MCD IDE controllers

84h Detect and install external parallel ports

85h Initialize PC-compatible PnP ISA devices

86h Re-initialize onboard I/O ports

87h Configure Motherboard Configurable Devices

88h Initialize BIOS Data Area

89h Enable Non-Maskable Interrupts (NMIs)

8Ah Initialize Extended BIOS Data Area

8Bh Test and initialize PS/2

Checkpoint

Code

POST Routine Description