54

4 BIOS Overview

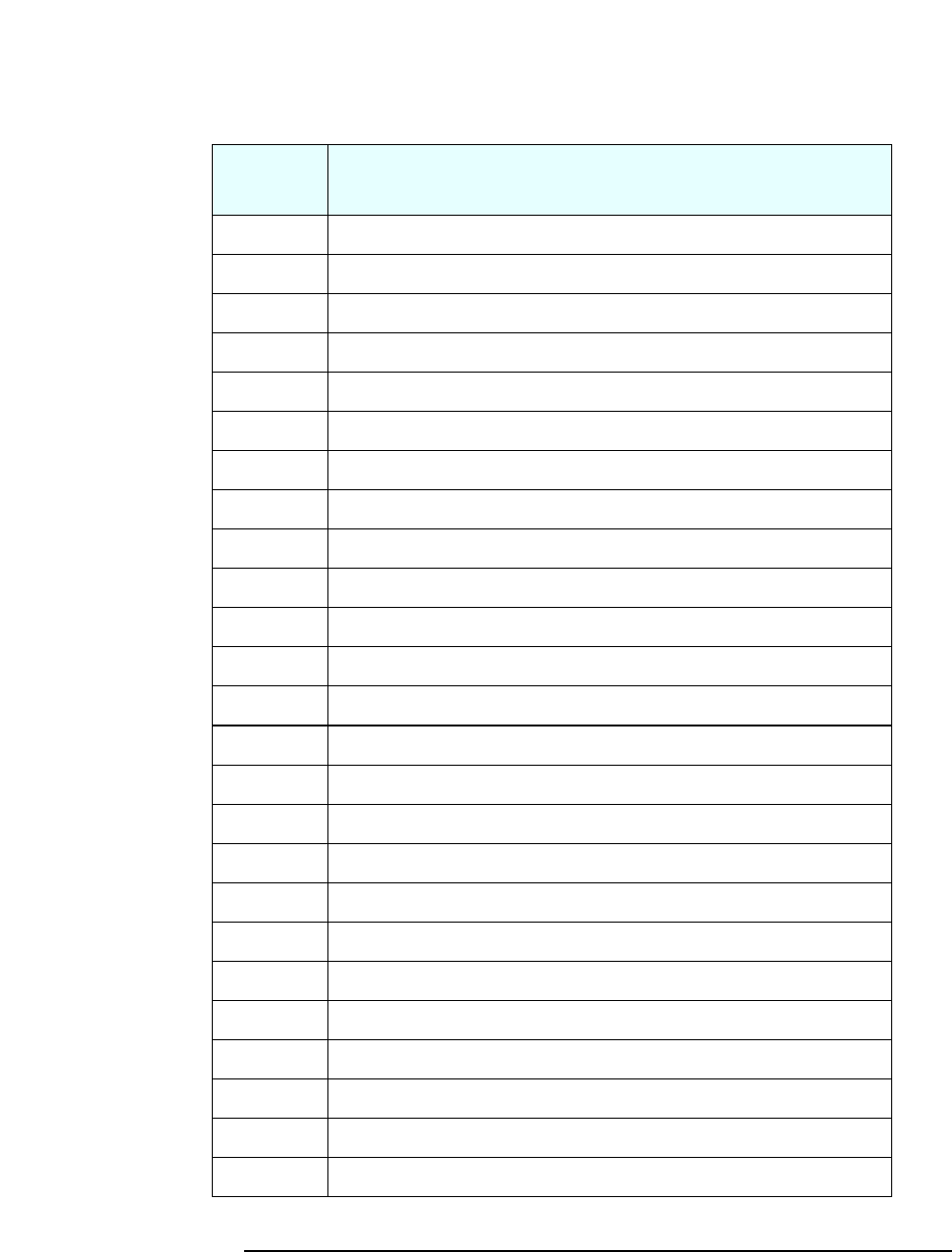

Order in Which the POST Tests are Performed

8Ch Initialize floppy controller

8Fh Determine number of ATA drives

90h Initialize hard disk controllers

91h Initialize local-bus hard disk controllers

92h JumptoUsersPatch2

93h Build MPTABLE for multi-processor boards

94h Disable A20 address line (Rel. 5.1 and earlier)

95h Install CD ROM for boot

96h Clear huge ES segment register

97h Fixup Multi Processor table

99h Check for SMART drive

9Ah Shadow option ROMs

9Ch Set up Power Management

9Eh Enable hardware interrupts

9Fh Determine number of ATA drives

A0h Set time of day

A2h Check key lock

A4h Initialize typematic rate

A8h Erase F2 prompt

AAh Scan for F2 key stroke

ACh Enter SETUP

AEh Clear IN POST flag

B0h Check for errors

B2h POST done - prepare to boot operating system

B5H Terminate QuietBoot

Checkpoint

Code

POST Routine Description