Documentation Changes

22 Intel

®

80303 and 80302 I/O Processors Specification Update

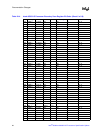

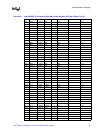

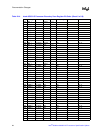

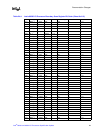

"42 (BC_1, *, control, 1)," &

"43 (BC_1, i_rstz, output3, X, 111, 1, Z)," &

"44 (CBSC_1, GPIO(3), bidir, X, 45, 1, Z)," &

"45 (BC_1, *, control, 1)," &

"46 (CBSC_1, GPIO(4), bidir, X, 47, 1, Z)," &

"47 (BC_1, *, control, 1)," &

"48 (CBSC_1, GPIO(5), bidir, X, 49, 1, Z)," &

"49 (BC_1, *, control, 1)," &

"50 (CBSC_1, GPIO(6), bidir, X, 51, 1, Z)," &

"51 (BC_1, *, control, 1)," &

"52 (CBSC_1, GPIO(7), bidir, X, 53, 1, Z)," &

"53 (BC_1, *, control, 1)," &

"54 (BC_4, irqz(0), input, X)," &

"55 (BC_4, irqz(1), input, X)," &

"56 (BC_4, irqz(2), input, X)," &

"57 (BC_4, irqz(3), input, X)," &

"58 (BC_4, irqz(4), input, X)," &

"59 (BC_4, irqz(5), input, X)," &

"60 (BC_1, nc2, output3, X, 65, 1, Z)," &

"61 (BC_4, lcdinitz, input, X)," &

"62 (BC_4, logic1, input, X)," &

"63 (BC_1, failz, output3, X, 110, 1, Z)," &

"64 (BC_4, nmiz, input, X)," &

"65 (BC_1, *, control, 1)," &

"66 (BC_4, nc3, input, X)," &

"67 (BC_4, nc4, input, X)," &

"68 (BC_4, nc5, input, X)," &

"69 (BC_4, nc6, input, X)," &

"70 (BC_4, nc7, input, X)," &

"71 (BC_4, nc8, input, X)," &

"72 (BC_4, nc9, input, X)," &

"73 (BC_4, nc10, input, X)," &

"74 (BC_4, nc11, input, X)," &

"75 (BC_4, nc12, input, X)," &

"76 (BC_4, nc20, input, X)," &

"77 (BC_4, nc13, input, X)," &

"78 (BC_4, nc15, input, X)," &

"79 (BC_4, nc14, input, X)," &

"80 (BC_4, nc16, input, X)," &

"81 (BC_4, pwrdelay, input, X)," &

"82 (BC_1, nc17, output3, X, 65, 1, Z)," &

"83 (BC_1, nc19, output3, X, 65, 1, Z)," &

"84 (BC_1, nc18, output3, X, 85, 1, Z)," &

"85 (BC_1, *, control, 1)," &

"86 (BC_1, dclk(3), output3, X, 111, 1, Z)," &

"87 (BC_1, dclk(2), output3, X, 111, 1, Z)," &

"88 (BC_1, dclk(1), output3, X, 111, 1, Z)," &

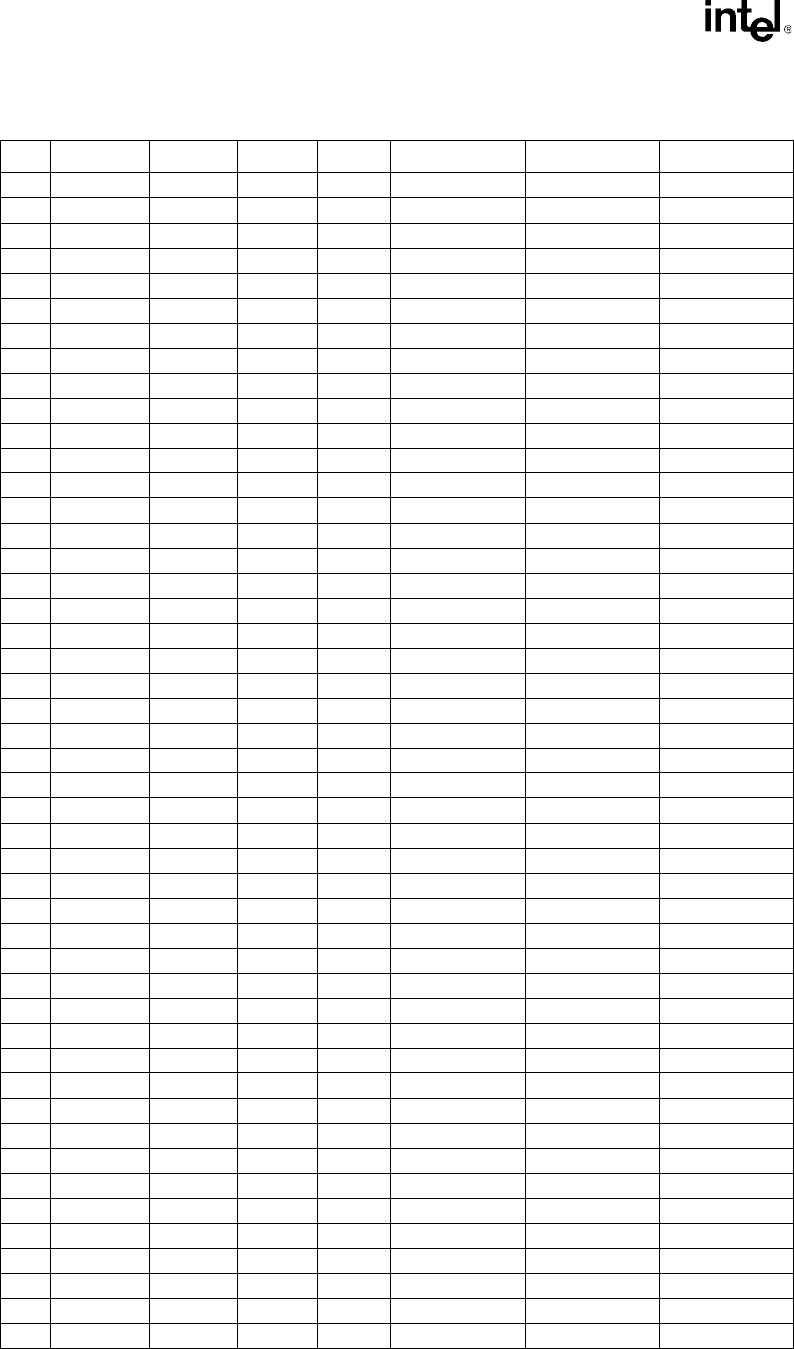

Table 24-4. Intel® 80303 I/O Processor Boundary Scan Register Bit Order (Sheet 2 of 10)

# Cell Type Name Function Safe bit Control Signal Disable Value Disable Result