Intel

®

80303 and 80302 I/O Processors Specification Update 33

Documentation Changes

13. Section 1.2.2 on page 1-2 has incorrect data

Problem: The second sentence of the first paragraph is incorrect. It states the Internal Bus operates at

66 MHz. It is actually 100 MHz.

Workaround: Change the second sentence to the following:

“The Internal Bus operates at 100 MHz and is 64 bits wide.”

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

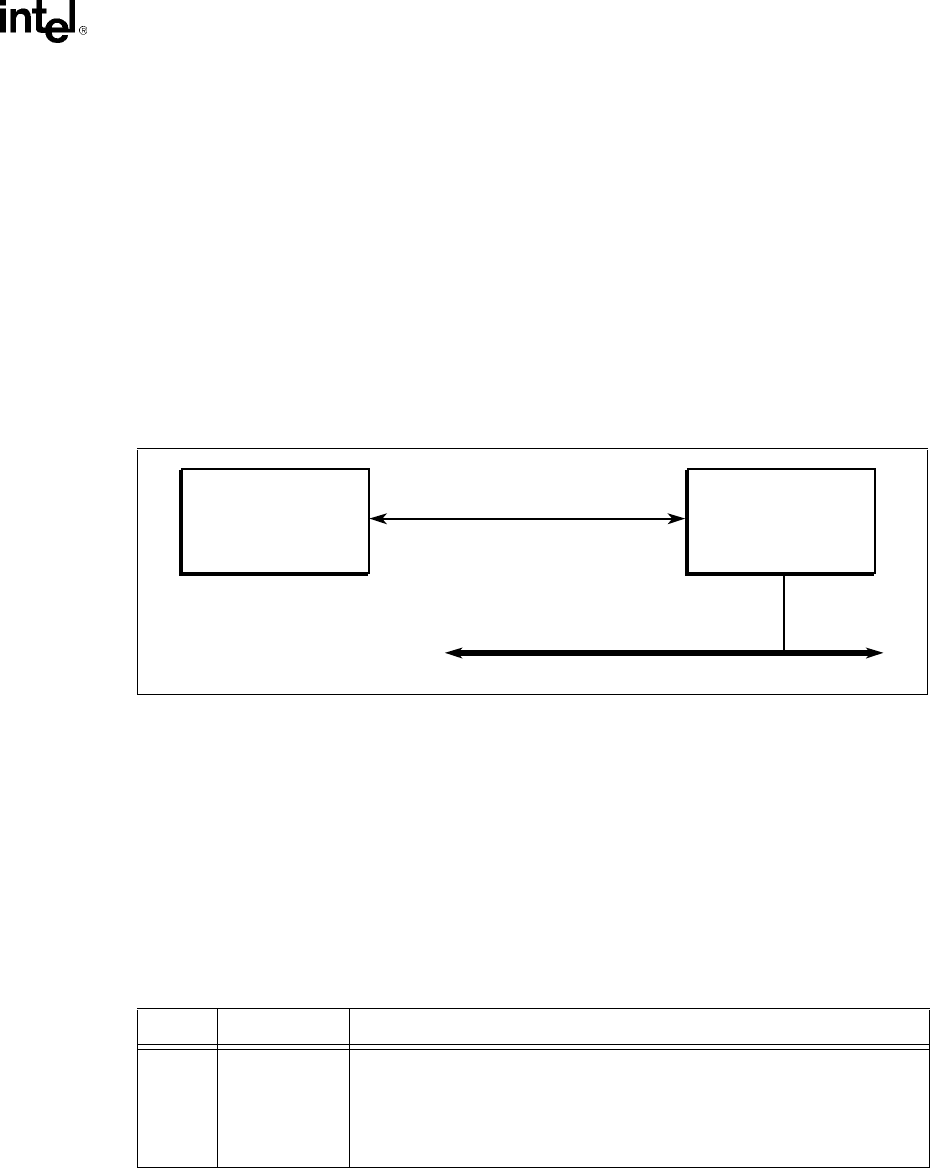

14. Figure 12-2 on page 12-10 has incorrect data

Problem: The Internal bus in diagram shows 66 MHz bus speed. The actual bus speed is 100 MHz

Workaround: Replace Figure 12-2 with the following:

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

15. Section 19.1 on page 19-1 has incorrect data

Problem: The last bullet incorrectly states, '64-bit/66MHz PCI and 80303 I/O processor internal bus

interface.' The internal bus on the 80303 I/O processor is 100 MHz.

Workaround: Change the last bullet to the following: '64-bit/66MHz PCI and 64-bit/100 MHz internal bus

interface.'

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

16. Table 14-46 on page 14-109 has missing data

Problem: Table 14-46 is missing the bit description for bit 12. Add the following:

Workaround: When clear, the Special Downstream Memory window is closed.

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

Figure 12-2. Core Processor/BIU Interface Block Diagram

Bit Default Description

12

Varies with

inverse of the

external state of

RAD[2]/SPME

M# at Primary

PCI bus reset

Special Downstream Window Enable - When set, a special downstream

memory window which includes the addresses FEC0_0000h through

FECF_FFFFh is opened. This window provides support for an alternate address

mechanism to a Hot-Plug Controller.

A6414-02

100 MHz Intel i960 Processor Local Bus

100 MHz

Intel

®

i960

®

Core Processor

Bus Interface

Unit

100 MHz Internal Bus (IB)