Documentation Changes

32 Intel

®

80303 and 80302 I/O Processors Specification Update

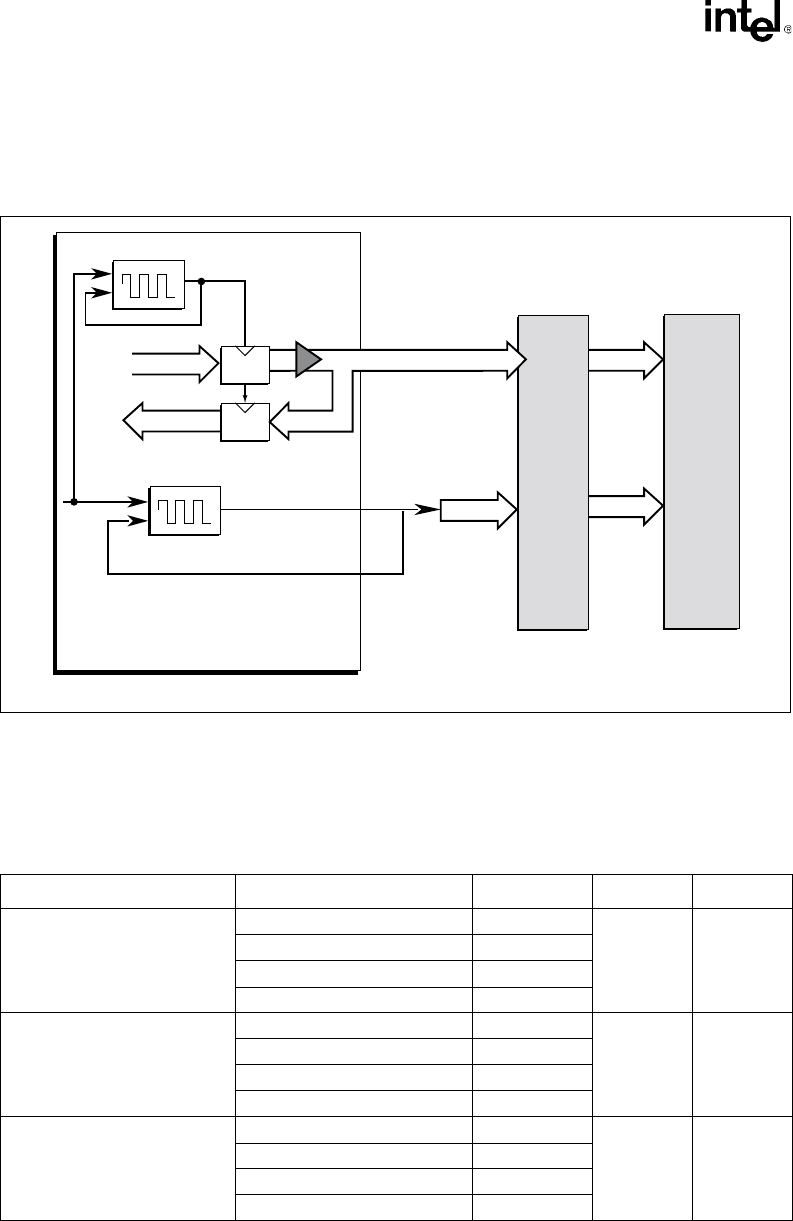

11. Figure 25-2 on pg 25-2 did not print correctly

Problem: Figure 25-2 on pg 25-2 did not print correctly.

Workaround: Replace Figure 25-2 with the following:

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual.

12. Table 25-2 on page 25-3 did not print completely

Problem: Table 25-2 on page 25-3 did not print completely

Workaround: Replace Table 25-2 with the following:

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

Input Clock Region/Clock Buffered/PLL P_M66EN S_M66EN

P_CLK = 33 MHz

Region 1: 1x P_CLK Buffered

0 0

Region 2: 3x P_CLK PLL

Region 3: 3x P_CLK PLL

Region 4: 1x P_CLK Buffered

P_CLK = 66 MHz

Region 1: 1x P_CLK Buffered

11

Region 2: 3/2x P_CLK PLL

Region 3: 3/2x P_CLK PLL

Region 4: 1x P_CLK Buffered

P_CLK = 66 MHz

Region 1: 1x P_CLK Buffered

10

Region 2: 3/2x P_CLK PLL

Region 3: 3/2x P_CLK PLL

Region 4: 1/2x P_CLK Buffered

NOTE: Combination of P_M66EN=0 and S_M66EN=1 is not supported by the Intel

®

80303 I/O processor.

When P_M66EN=0, the 80303 I/O processor forces S_M66EN=0 ensuring the unsupported condition

never occurs.

A4662-02

SDRAM

DIMM0

DQ(71:0)

I_CLK

P_CLK

DCLKin

DQ(71:0)

DCLKout

SDQ(71:0) SDQ(71:0)

CLK(3:0)

CLK(3:0)

SDRAM

DIMM1