Intel

®

80303 and 80302 I/O Processors Specification Update 31

Documentation Changes

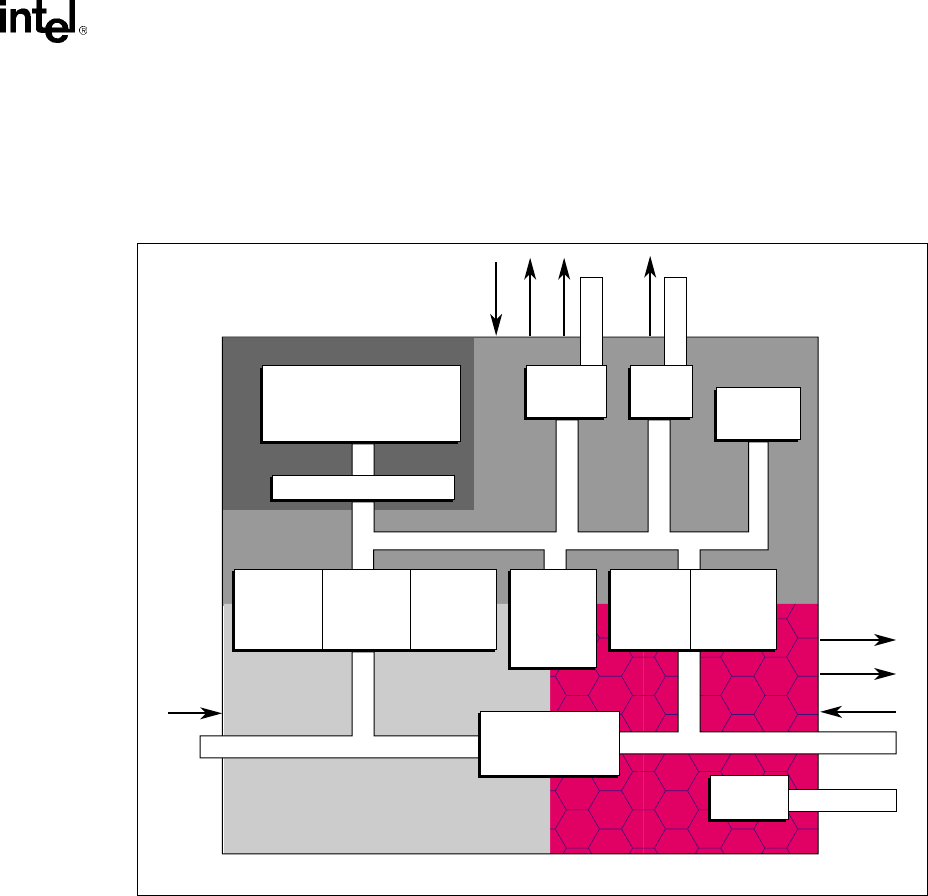

9. Figure 25-1 on pg 25-1 has incorrect data

Problem: The Internal bus in diagram shows 66 MHz bus speed. The actual bus speed is 100 MHz

Workaround: Replace Figure 25-1 with the following:

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

10. Section 25.1.3 on page 25-2

Problem: The third sentence of the first paragraph is incorrect. It states the maximum bus speed of the region

is 66 MHz. It is actually 100 MHz.

Workaround: Change the third sentence to the following:

“It supports clock frequencies up to a maximum of 100 MHz.”

Affected Docs: Intel

®

80303 I/O Processor Developer’s Manual

Figure 25-1. Intel

® 80303 I/O Processor Clocking Regions Diagram

A8053-01

P_CLK

R_CLKOUT

R_CLKIN

S_CLKOUT

[5:0]

Intel

®

i960

®

JN CPU 100 MHz

16K I-Cache

4K D-Cache

Clock Region 3

Clock Region 1

Clock Region 2

Clock Region 4

Application

Accelerator

800 MBs Internal Bus (100MHz/64-bit)

64-Bit I/F

I

2

C Bus

Performance

Monitoring

Unit

Memory

Controller

I

2

C

Unit

DCLKOUT

DCLK[3:0]

SCL

DCLKIN

Bus Interface Unit

6 Reg/Gnt Pairs

Primary PCI Bus

2 Channel

DMA

Controller

Primary

Address

Translation

Unit

PCI - to - PCI

Bridge

I

2

0

Messaging

Unit

Secondary PCI Bus

Secondary

Address

Translation

Unit

1 Channel

DMA

Controller

Secondary

PCI Arbiter