Software Developer’s Manual 169

Ethernet Interface

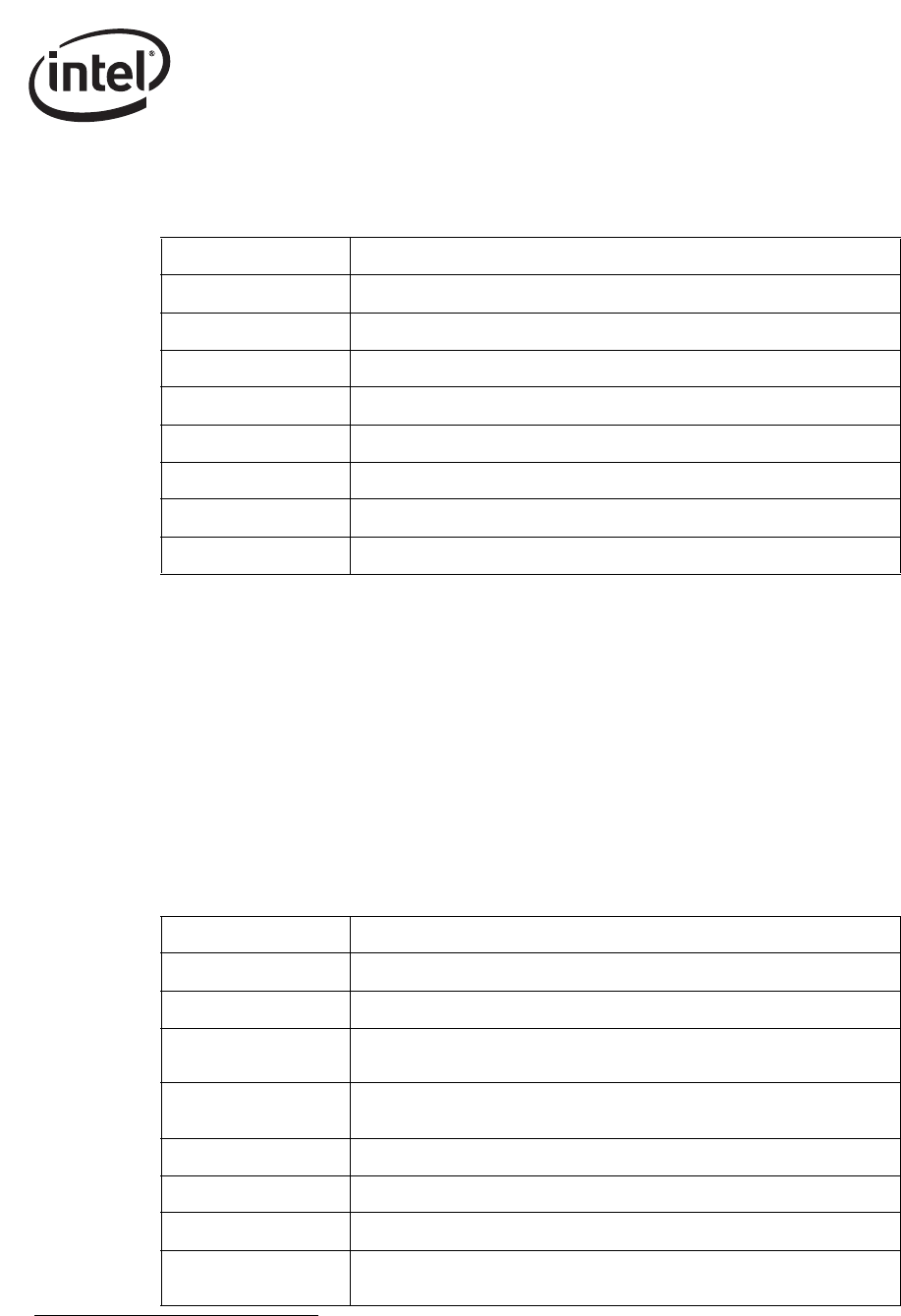

Table 8-5. Internal Serdes Mode

1

– Auto-Negotiation Skipped

TXCW.ANE = 0b

8.6.4 Internal PHY Mode Control Bit Resolution

Tables 8-6, 8-7, 8-8, and 8-9 list how Auto-Negotiation affects control bits in the Ethernet

Controller.

Refer to IEEE 802.3z, clause 37 for information related duplex and flow control link resolution per

the 802.3z Auto-Negotiation method. The Ethernet controller fully complies to the specified

resolution functions.

Table 8-6. GMII/MII Mode – PHY Speed Indication

CTRL.FRCSPD = CTRL.ASDE = CTRL.FRCDPLX = 0b

1. TBI for the 82544GC/EI.

Control Bit Effect on Control Bits

CTRL.FD Duplex is set by software for the desired mode of operation

CTRL.SLU Set by software

CTRL.RFCE Set by software for the desired mode of operation

CTRL.TFCE Set by software for the desired mode of operation

CTRL.SPEED No impact; speed always 1000 Mb/s in Internal SerDes

a

mode

STATUS.FD Reflects the value of CTRL.FD

STATUS.LU Reflects CTRL.SLU and internal link indication

STATUS.SPEED Internal SerDes

a

Mode is always 1000 Mb/s; fixed at 10b

a. TBI for the 82544GC/EI.

Control Bit Effect on Control Bits

CTRL.FD Duplex is set per internal signal after link up assertion by PHY.

CTRL.SLU Software should set to allow PHY to control.

CTRL.RFCE

Must be set by software after reading flow control resolution from MII

registers.

CTRL.TFCE

Must be set by software after reading flow control resolution from MII

registers.

CTRL.SPEED Ignored; no impact on speed.

STATUS.FD Reflects the value of CTRL.FD as above.

STATUS.LU Reflects link status and SLU set.

STATUS.SPEED

Speed status bits reflect speed resolved from speed indication inputs from

PHY.