82 Software Developer’s Manual

PCI Local Bus Interface

4.1.2 Reserved and Undefined Addresses

Any PCI or PCI-X register address space not explicitly declared in this specification should be

considered to be reserved, and should not be written. Writing to reserved or undefined

configuration register addresses can cause indeterminate behavior. Reads from reserved or

undefined configuration register addresses can return indeterminate values.

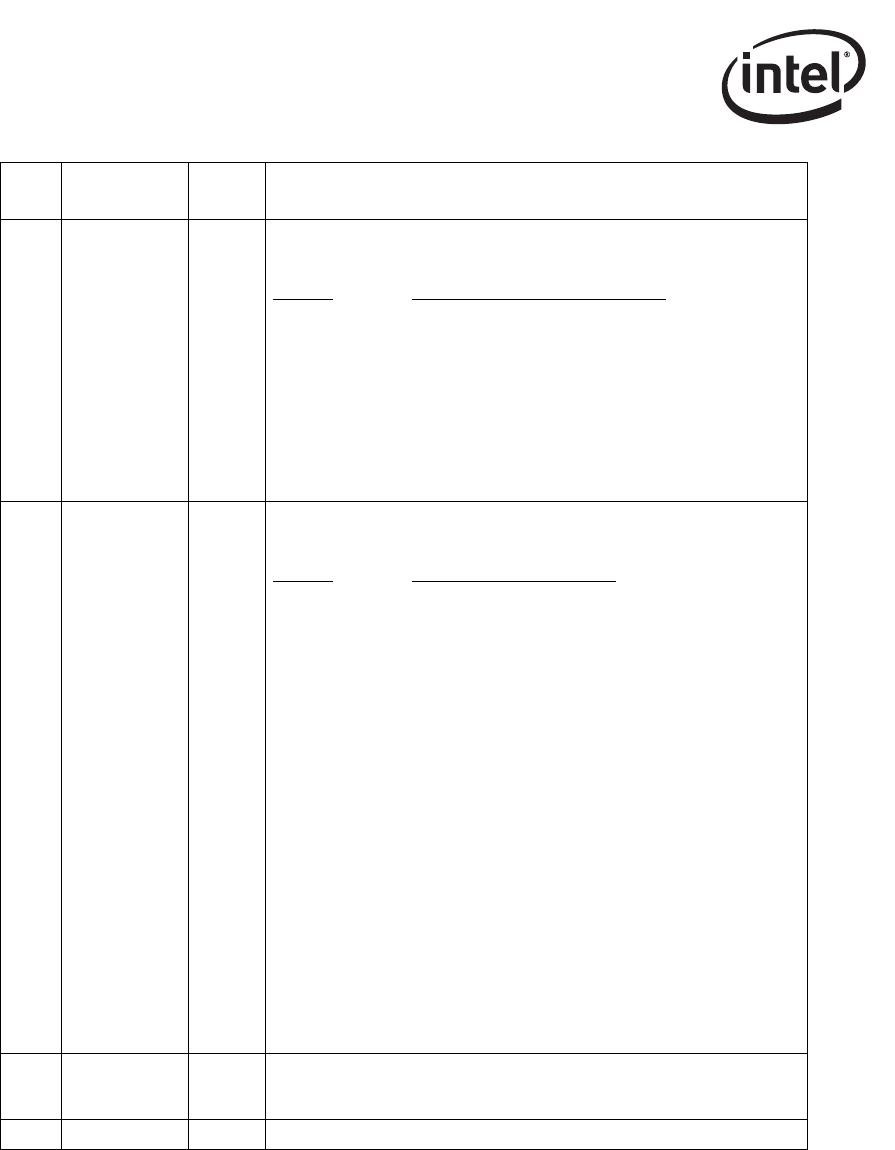

25:23 R 0b

Designed Maximum Outstanding Split Transactions. A 0b indicates that

the Ethernet controller is designed to have at the most one outstanding

transaction.

Register

Maximum Outstanding Transactions

0 1

1 2

2 3

3 4

4 8

5 12

6 16

7 32

28:26 R

0b

a

(see Description)

Designed Maximum Cumulative Read Size. Indicates a number that is

greater or equal maximum cumulative outstanding bytes to be read at one

time.

Register

Maximum Outstanding Bytes

0 1 KB

1 2 KB

2 4 KB

3 8 KB

4 16 KB

5 32 KB

6 64 KB

7 128 KB

The value of this register depends on the DMCR_Map and Max_Read bits

in the EEPROM’s Initialization Control Word 2 (see Section 5.6.12).

• DMCR_Map = 0b:

The value of this register reflects the number of bytes programmed in the

Maximum Memory Read Byte Count (MMRBC) field of the PCI-X

Command Register as follows:

• MMRBC = 0 (512) - DMCRS = 0 (1KB)

• MMRBC = 1 (1K) - DMCRS = 0 (1KB)

• MMRBC = 2 (2K) - DMCRS = 1 (2KB)

• MMRBC = 3 (4K) - DMCRS = 2 (4KB)

• DMCR_Map = 1b and Max_Read = 0b: DMCRS = 1 (2KB)

• DMCR_Map = 1b and Max_Read = 1b: DMCRS = 2 (4KB)

29

Read, write 1b

to clear

0b

Received Split Completion Error Message. This bit is set if the Ethernet

controller receives a Split Completion Message with the Split Completion

Error attribute bit set.

31:30 R 0b Reserved. Reads as 0b

a. Loaded from EEPROM.

Bits

Read/

Write

Intial

Value

Description