Software Developer’s Manual 329

Register Descriptions

13.5.2 Receive Address Low

RAL (05400h + 8*n; R/W)

16 registers contain the lower bits of the 48-bit Ethernet address. All 32 bits are valid. Software can

access the High and Low registers as a register pair if it can perform a 64-bit access to the PCI bus.

The addresses stored in these registers are used for unicast/multicast address filtering.

The first receive address register (RAL0, RAH0) is also used for exact match PAUSE frame

checking (Valid PAUSE packet that is addressed to the station’s address). Therefore, RAL0 and

RAH0 always should be used to store the individual Ethernet MAC address of the Ethernet

controller.

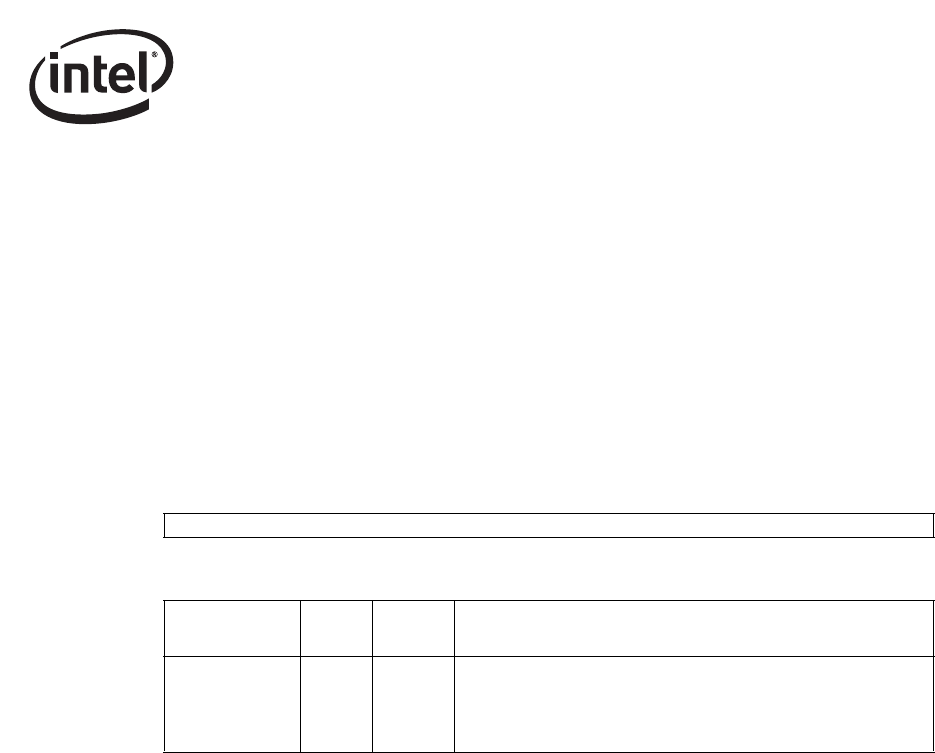

Table 13-90. RAL Register Bit Description

13.5.3 Receive Address High

RAH (05404h + 8n; R/W)

16 registers contain the upper bits of the 48-bit Ethernet address. The complete address is {RAH,

RAL}. Software can access the High and Low registers as a register pair if it can perform a 64-bit

access to the PCI bus. The addresses stored in these registers are used for unicast/multicast address

filtering.

The first receive address register (RAL0, RAH0) is also used for exact match Pause frame

checking (Valid Pause packet that is addressed to the station’s address). Therefore, RAL0 and

RAH0 always should be used to store the individual Ethernet MAC address of the Ethernet

controller.

Note: When writing to this register, always write low-to-high. When clearing this register, always clear

high-to-low.

31 0

RAL

Field Bit(s)

Initial

Value

Description

RAL 31:0 X

Receive address low

Contains the lower 32-bit of the 48-bit Ethernet address.

RAL0 should be used to store the lower 32-bit of the Ethernet

controller’s Ethernet MAC address.