Software Developer’s Manual 281

Register Descriptions

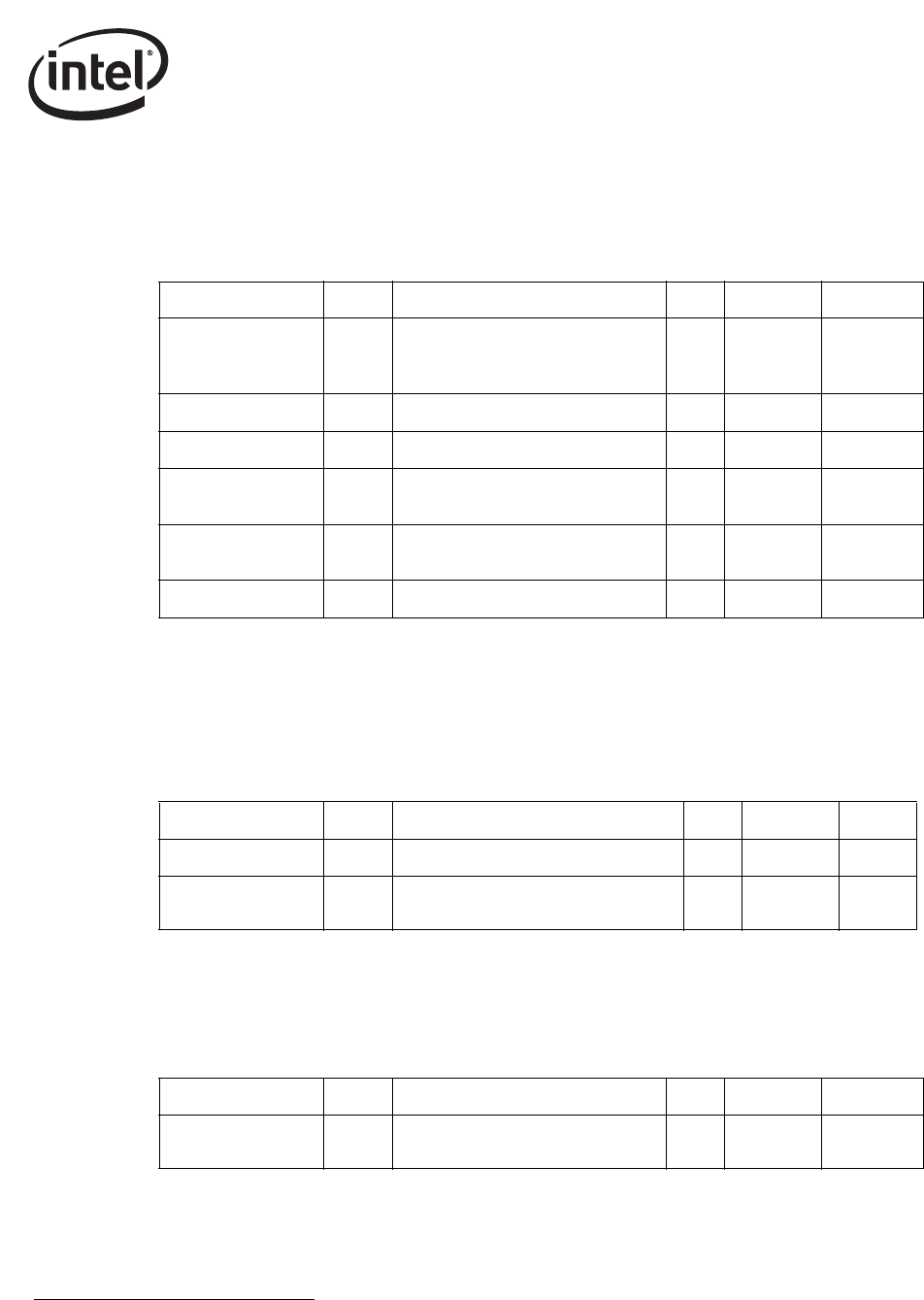

13.4.7.1.23 Extended PHY Specific Control Register 2

EPSCON2 (26d; R/W)

NOTE: Not applicable to the 82540EP/EM, 82544GC/EI, 82541xx, or 82547GI/EI.

13.4.7.1.24 Extended PHY Specific Status Register (82544GC/EI Only)

EPSSTAT (27d; R)

13.4.7.1.25 MDI Register 30 Page Select

1

R30PS (29d; WO)

Table 13-47. Extended PHY Specific Control Register 2 Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Fiber Output

Amplitude

2:0

111b = 1.2, 100b = 0.9, 001b = 0.6

110b = 1.1, 011b = 0.8, 000b = 0.5

101b = 1.0, 010b = 0.7

R/W 100b Retain

Reserved 3 Reserved. Should be set to 1b. R/W 1b 1b

Reserved 4 Reserved. Should be set to 0b. R/W 0b 0b

Fiber Output

Impedance

5

1b= 75 ohm.

0b = 50 ohm.

R/W 0b Update

Fiber Input

Impedance

6

1b = 75 ohm.

0b = 50 ohm.

R/W 0b Update

Reserved 15:7 Reserved. Should be set to 0b. R/W 000h 000h

Table 13-48. Extended PHY Specific Status Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

MODE[3:0] 27.3:0 MODE[3:0]. RO MODE[3:0] Retain

Reserved 27.15:4

Reserved. Should be set to

000000000000b.

RO 0b 0b

1. Not applicable to the 82544GC/EI, 82541xx, or 82547GI/EI.

Table 13-49. MDI Register 30 Page Select Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Register 30 Page

Select

15:0

Selects the register accessible via the

“window” at MDI register 30.

R/W 0000h 0000h