Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 95

Host Software Interface

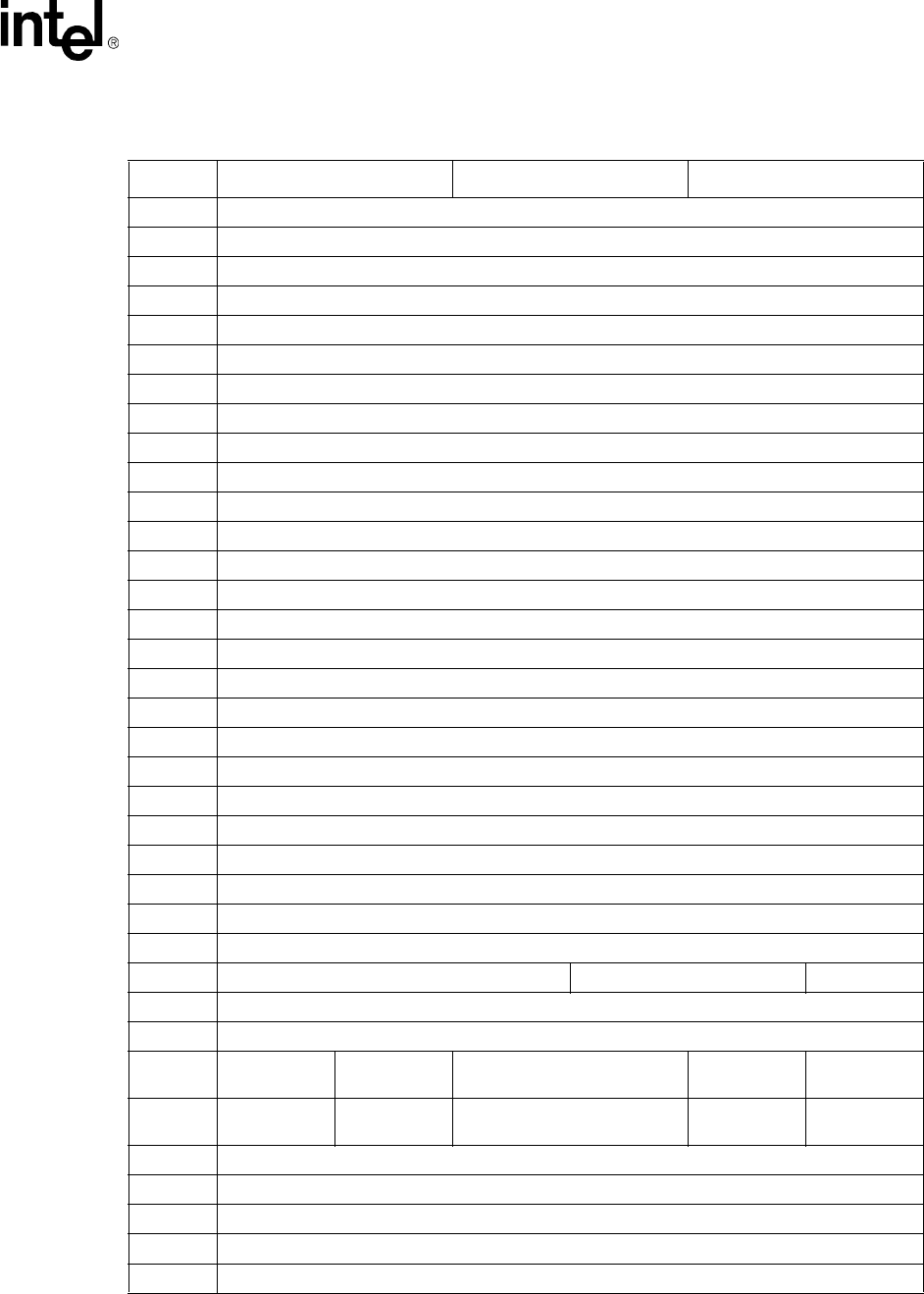

Table 51. Dump Data Dwords (20-148)

Dword Byte 3 Byte 2 Byte 1

20 – 29 Reserved

30 Micromachine (MM) Register File 39

31 Micromachine (MM) Register File 38

32 Micromachine (MM) Register File 37

33 Micromachine (MM) Register File 36

34 Micromachine (MM) Register File 35

35 Micromachine (MM) Register File 34

36 Micromachine (MM) Register File 33

37 Micromachine (MM) Register File 32

38 Receive Short Frame Errors

39 Receive CDT Errors Counter

40 Receive Overrun Errors Counter

41 Receive Resource Errors Counter

42 Receive Alignment Errors Counter

43 Receive CRC Errors Counter

44 Receive Good Frames Counter

45 Transmit Total Collisions Counter

46 Transmit Multiple Collisions Counter

47 Transmit Single Collisions Counter

48 Transmit Deferred Counter

49 Transmit Lost CRS Counter

50 Transmit Underrun Errors Counter

51 Transmit Late Collisions Errors Counter

52 Transmit Maximum Collisions Errors Counter

53 Transmit Good Frames Counter

54 – 64 Reserved

65 Reserved Execution Status Port

66 SCB Port Register

67 SCB Pointer register

68

SCB Interrupt

Mask Byte

SCB CUC and

RUC Byte

SCB Interrupt Byte

SCB CUS and

RUS Byte

69

SCB Interrupt

Mask Byte

SCB CUC and

RUC Byte

SCB Interrupt Byte

SCB CUS and

RUS Byte

70 – 81 Reserved

82 DMA Arbitration Registers

83 – 85 Reserved

86 Micromachine Register File 31

87 Micromachine Register File 30