68 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

• BYTE 2: Adaptive IFS. This byte indicates the minimum number of PCI clocks counted

between sending two transmit frames on the wire. The resolution of this counter is 8 PCI

clocks making the range from 0 to 2040 PCI clocks.

Default - 0.

Recommended - 0.

• BYTE 3.

— Bit 3 - Terminate Write on Cache Line. This bit is reserved on the 82557 and should be set

to 0.

However, when this bit is set on the 82558 or a later generation controller, the device

attempts to terminate its write accesses on cache lines. This may yield lower PCI

throughput in systems which are not extremely cache line oriented. This bit should

therefore be set only in systems that are extremely cache line oriented.

0 = Terminate Write on Cache Line disabled.

1 = Terminate Write on Cache Line enabled.

Default - 0 (Terminate Write on Cache Line disable).

Recommended - 0.

— Bit 2 - Read Alignment Enable. This bit is reserved on the 82557 and should be set to 0.

However, when this bit is set on the 82558 and later generation controllers, the device

attempts to align its read accesses to cache lines. This may yield lower PCI throughput in

systems that are not extremely cache line oriented. Thus, this bit should be set only in

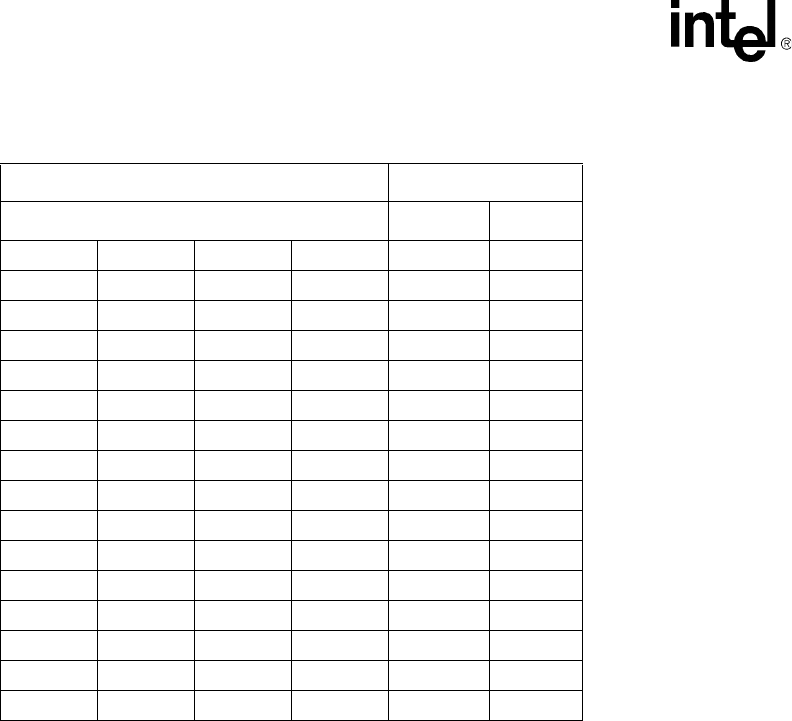

Table 44. 82558 and 82559 Dual-Port FIFO Settings - Receive

Configuration Value (Nibble Wide) Receive FIFO Limit

Binary (Receive Bits 3:0) Dwords Bytes

0 0 0 0 32 128

0 0 0 1 30 120

0 0 1 0 28 112

0 0 1 1 26 104

0 1 0 0 24 96

0 1 0 1 22 88

0 1 1 0 20 80

0 1 1 1 18 72

1 0 0 0 16 64

a

a. This line represents the default values.

1 0 0 1 14 56

1 0 1 0 12 48

1 0 1 1 10 40

1 1 0 0 8 32

1 1 0 1 6 24

1 1 1 0 4 16

1 1 1 1 2 8