20 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

PCI Interface

While wake-up events are not allowed in the D0 power state, hardware does not automatically

preclude this functionality. To ensure that wake-up events are not generated when in D0, software

must clear the PME Enable bit when putting the device into that state. To ensure that no spurious

wake-up events are generated by the function, the PME Status bit (in the PMDR register or the

PMCSR) must be specifically cleared (by writing a 1) when the PME Enable bit is set.

To support Wake on LAN mode (pre-boot wake), the PME Enable and PME Status bits are set with

known values after power-up reset. The ALTRST# pin should be connected to the device auxiliary

power good signal on the motherboard so that it will be active low on system power up. Assertion

of ALTRST# clears the PME Status bit and sets the PME Enable bit if the clock is active on the

CLK pin. Thus, if the Wake on LAN (WOL) bit in the EEPROM is set, the device will wake up the

system upon receiving of Magic Packet*.

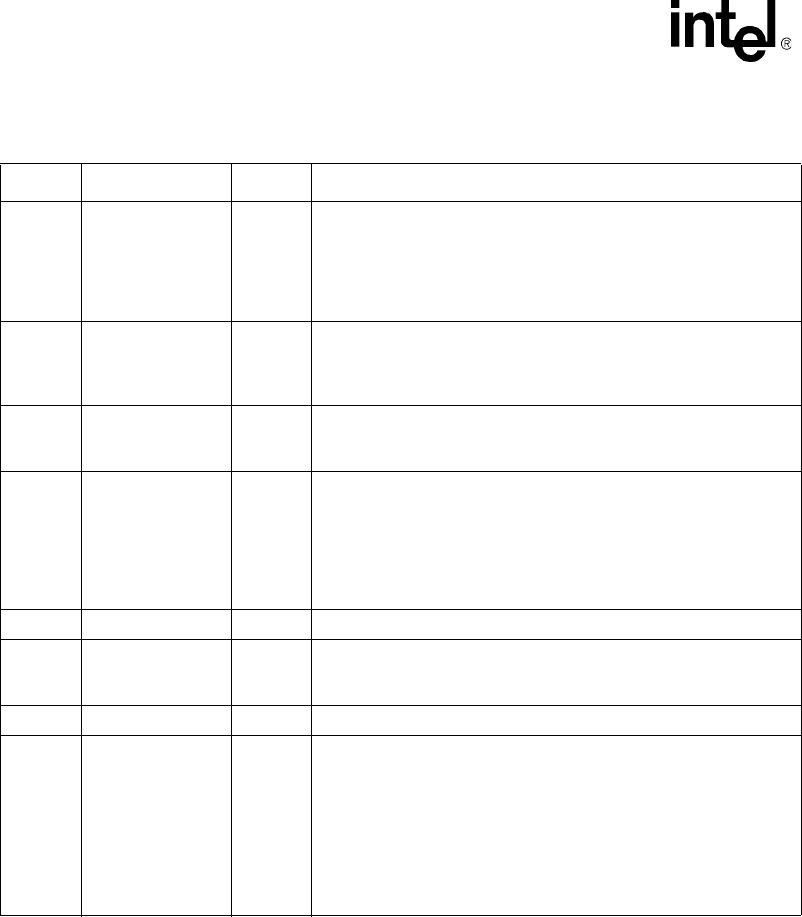

Table 5. Power Management Control/Status Register

Bit Value at Reset R / W Description

15

82558A: 0

82558B, 82559:

no auxiliary power

- 0

Sticky bit

Read

Clear

PME Status. This bit is set upon a wake-up event from the link. It is

independent of the state of the PME_Enable bit. When software

writes 1 to this bit it is cleared and the device stops asserting PME#

(if enabled).

14:13

82558: 00

82559: 10 or 00

RO

Data Scale. The Data Scale is not supported on the 82558 and

always returns 0. For the 82559, it is a 2-bit read-only field

indicating the data register scaling factor. For the 82559, it equals

10b for registers 0 through 8 and 00b for registers 9 through 15.

12:9 0000 R/W

Data Select. This 4-bit field selects which data is reported through

the Data Register and Data Scale field. This register is only

supported on the 82559 and later generation devices.

8

82558A = 0

82558B & 82559

= 0

Unknown

(0 if no auxiliary

power available)

Read

Clear

PME Enable. This bit enables the device to assert PME#.

7:5 000 Reserved.

40 RO

Dynamic Data. The 82558 does not implement this register and

returns 0. The 82559 does not support the ability to monitor power

consumption dynamically.

3:2 00 RO Reserved.

01:00 00 R/W

Power State. This 2-bit field is used both to determine the current

power state of the 82258 or 82559 and to set the 82558 or 82559

into a new power state. The definition of the field values is given

below.

00b - D0

01b - D1

10b - D2

11b - D3