4800-180001 - 42x4MB / 32MB42004966550 (9409-M50)

4300-83001 - 22x4MB / 0MB42005634520 (9408-M25)

430012x4MB / 0MB42005633520 (9407-M15)

Processor

CPW

CPU

(2)

Range

L2/L3 cache

(1)

per chip

Chip Speed

MHz

Processor

Feature

Model

Table C.3.1. CPW values for Power System Models

*Note: 1. These models have a dedicated L2 cache per processor core, and share the L3 cache

between two processor cores.

2. The range of the number of processor cores per system.

C.3.2 CPW values for IBM BladeCenter JS12 - IBM i operating system

71001.8 of 22x4MB / 0 MB380052BFJS12 (7998-60X)

Processor

CPW

(3)

CPUs

(2)

L2/L3 cache

(1)

per chip

Chip Speed

MHz

Processor

Feature

Blade Model

Table C.3.2. IBM BladeCenter models

*Note: 1. These models have a dedicated L2 cache per processor core, and no L3 cache

2. CPW value is for a 1.8-core partition with shared processors and a 0.2-core VIOS partition

3. The value listed is unconstrained CPW (there is sufficient I/O such that the processor would be

the first constrained resource). The I/O constrained CPW value for a 12-disk configuration is

approximately 1200 CPW (100 CPW per disk).

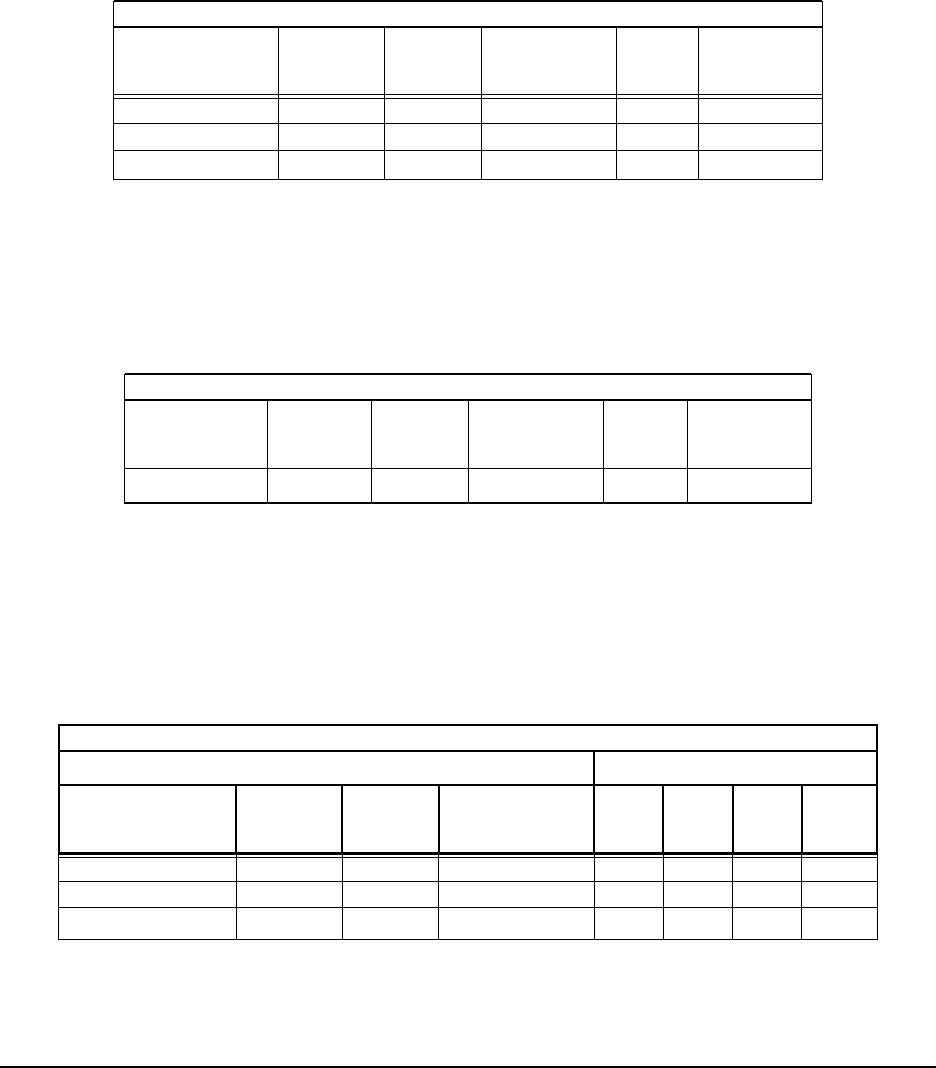

C.3.3 CPW values for IBM Power Systems - IBM i operating system

769004010021200108002x4MB / 32MB47007380570 (9117-MMA)

68600355001920096502x4MB / 32MB42005621/5622570 (9117-MMA)

57600301001610081502x4MB / 32MB35005620570 (9117-MMA)

16 cores8 cores4 cores2 cores

L2/L3 cache

(1)

per chip

Chip Speed

MHz

Processor

Feature

Model

Processor CPW

Table C.3.3. CPW values for Power System Models

*Note: 1. These models have a dedicated L2 cache per processor core, and share the L3 cache

between two processor cores.

C.4 V6R1 Additions (January 2008)

C.4.1 IBM i5/OS running on IBM BladeCenter JS22 using POWER6 processor technology

IBM i 6.1 Performance Capabilities Reference - January/April/October 2008

© Copyright IBM Corp. 2008 Appendix C CPW, CIW and MCU for System i Platform 347