138003.7 of 4

(3)

2x4MB / 0 MB400052BEn/an/aJS22 (7998-61X)

110403 of 4

(2)

2x4MB / 0 MB400052BEn/an/aJS22 (7998-61X)

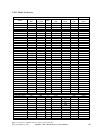

Processor

CPW

CPUs

L2/L3 cache

(1)

per chip

Chip Speed

MHz

Processor

Feature

Edition

Feature

Server

Feature

Blade Model

Table C.4.1. IBM BladeCenter models

*Note: 1. These models have a dedicated L2 cache per processor core, and no L3 cache

2. CPW value is for a 3-core dedicated partition and a 1-core VIOS

3. CPW value is for a 3.7-core partition with shared processors and a 0.3-core VIOS partition

C.5 V5R4 Additions (July 2007)

C.5.1 IBM System i using the POWER6 processor technology

24200-17200010800-769002 - 162x4MB / 32MB

4700

73807063

(3)

4924i570 (9406-MMA)

12300-897005500-401001 - 82x4MB / 32MB470073807058

(3)

4923i570 (9406-MMA)

12300-475005500-212001 - 42x4MB / 32MB470073807053

(3)

4922i570 (9406-MMA)

45000-17200020100-769004 - 162x4MB / 32MB4700738054624912i570 (9406-MMA)

24200-8970010800-401002 - 82x4MB / 32MB4700738054614911i570 (9406-MMA)

12300-475005500-212001 - 42x4MB / 32MB4700738054604910i570 (9406-MMA)

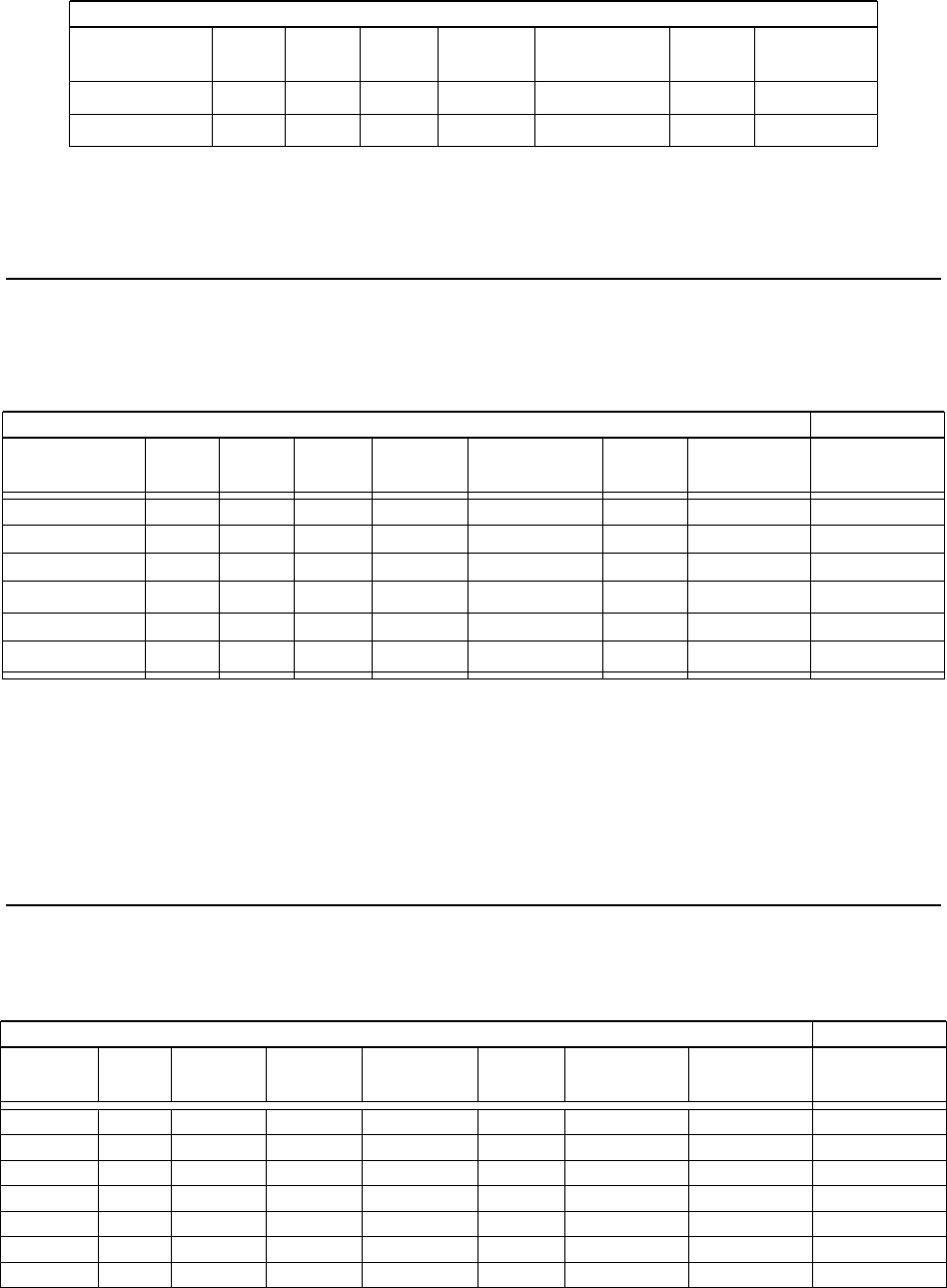

MCU

(4)

Processor

CPW

CPU

(5)

Range

L2/L3 cache

(1)

per chip

Chip Speed

MHz

Processor

Feature

Edition

Feature

2

Server

Feature

Model

Table C.5.1. System i models

*Note: 1. These models have a dedicated L2 cache per processor core, and share the L3 cache

between two processor cores.

2. This is the Edition Feature for the model. This is the feature displayed when you display

the system value QPRCFEAT.

3. Capacity Backup model.

4. Projected values. See Chapter 11 for more information.

5. The range of the number of processor cores per system.

C.6 V5R4 Additions (January/May/August 2006 and January/April 2007)

C.6.1 IBM System i using the POWER5 processor technology

68400

(7)

- 131

K

(7)

Per Processor

31500-588008-161.9/36MB2300NA58909406-595

35800

(7)

- 242

K

(7)

016000-1080004 - 321.9/36MB2300NA5876

(4)

9406-595

35800

(7)

- 242

K

(7)

Per Processor

16000-1080004 - 321.9/36MB2300NA5896

(4)

9406-595

131

K

(7)

- 242

K

(7)

061000-10800016 - 321.9/36MB2300NA58719406-595

131

K

(7)

- 242

K

(7)

Per Processor

61000-10800016 - 321.9/36MB2300NA58919406-595

242

K

(7)

- 460

K

(7)

0108000-216000

32 - 64

(8)

1.9/36MB2300NA58729406-595

242

K

(7)

- 460

K

(7)

Per Processor

108000-216000

32 - 64

(8)

1.9/36MB2300NA58929406-595

MCU

5250 OLTP

CPW

Processor

CPW

CPU

Range

L2/L3 cache

per CPU

(1)

Chip Speed

MHz

Accelerator

Feature

Edition

Feature

2

Model

Table C.6.1.1. System i models

IBM i 6.1 Performance Capabilities Reference - January/April/October 2008

© Copyright IBM Corp. 2008 Appendix C CPW, CIW and MCU for System i Platform 348