• Multiple frequency and voltage points for optimal performance and power

efficiency. These operating points are known as P-states.

• Frequency selection is software controlled by writing to processor MSRs. The

voltage is optimized based on the selected frequency and the number of active

processor cores.

— Once the voltage is established, the PLL locks on to the target frequency.

— All active processor cores share the same frequency and voltage. In a multi-

core processor, the highest frequency P-state requested among all active

cores is selected.

— Software-requested transitions are accepted at any time. If a previous

transition is in progress, the new transition is deferred until the previous

transition is completed.

• The processor controls voltage ramp rates internally to ensure glitch-free

transitions.

• Because there is low transition latency between P-states, a significant number of

transitions per-second are possible.

Low-Power Idle States

When the processor is idle, low-power idle states (C-states) are used to save power.

More power savings actions are taken for numerically higher C-states. However,

higher C-states have longer exit and entry latencies. Resolution of C-states occur at

the thread, processor core, and processor package level. Thread-level C-states are

available if Intel Hyper-Threading Technology is enabled.

Caution: Long term reliability cannot be assured unless all the Low-Power Idle States are

enabled.

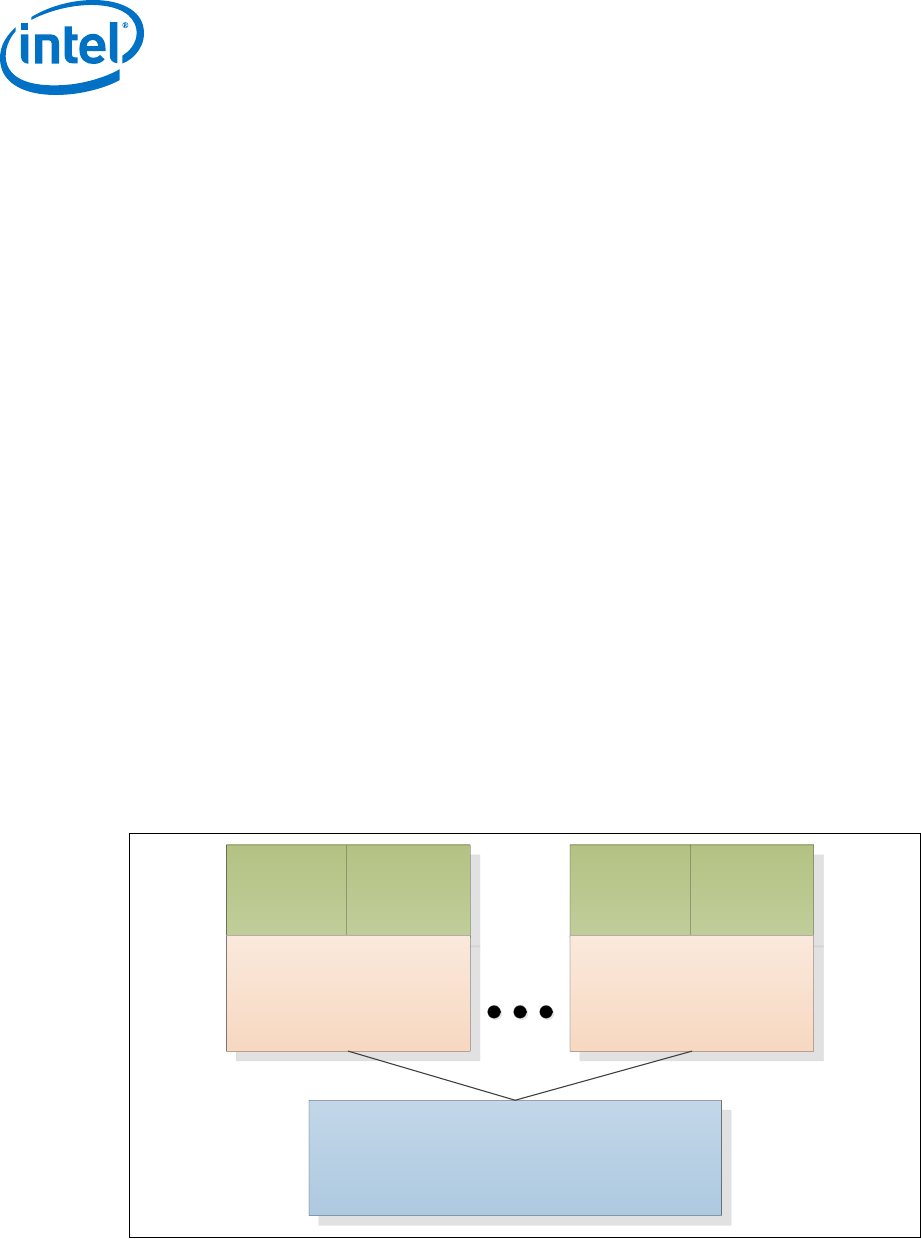

Figure 12. Idle Power Management Breakdown of the Processor Cores

Thread 0 Thread 1

Core 0 State

Thread 0 Thread 1

Core N State

Processor Package State

Entry and exit of the C-states at the thread and core level are shown in the following

figure.

4.2.2

Processor—Power Management

Desktop 4th Generation Intel

®

Core

™

Processor Family, Desktop Intel

®

Pentium

®

Processor Family, and Desktop Intel

®

Celeron

®

Processor Family

Datasheet – Volume 1 of 2 December 2013

52 Order No.: 328897-004