30

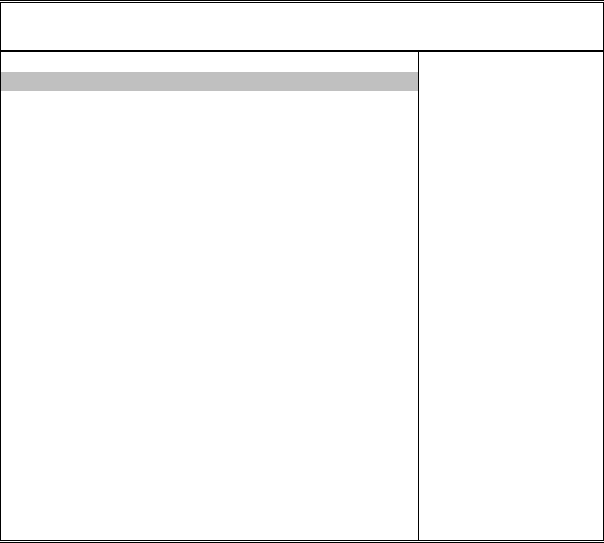

4.6 Advanced Chipset Setup

This section allows you to configure the system based on the specific

features of the installed chipset. This chipset manages bus speeds and

the access to the system memory resources, such as DRAM and the

external cache. It also coordinates the communications between the

conventional ISA and PCI buses. It must be stated that these items

should never be altered. The default settings have been chosen

because they provide the best operating conditions for your system.

You might consider and make any changes only if you discover that the

data has been lost while using your system.

AMIBIOS SETUP – ADVANCED CHIPSET SETUP

(C)2001 American Megatrends, Inc. All Rights Reserved

******** DRAM Timing ******** Available Options:

Configure SDRAM Timing by SPD Enabled

`

Disabled

SDRAM Frequency Auto Enabled

SDRAM CAS# Latency 2.5

SDRAM Bank Interleave Disabled

SDRAM Command Rate 2T

Memory Hole Disabled

Auto Prechrage for TLB/WB Disabled

Write Recovery time 2T

AGP Mode 4x

AGP Read Synchronization Disabled

AGP Fast Write Disabled

AGP Comp. Driving Auto

Manual AGP Comp. Driving CB

AGP Aperture Size 64MB

AGP Master 1 W/S Write Disabled

AGP Master 1 W/S Read Disabled

Search for MDA Resources Yes

PCI Delay Transaction Enabled

USB Controller 4 USB Ports

USB Device Legacy Support All Device

V-Link Data 2X Support Disabled ESC: Exit : Sel

PgUp/PgDn: Modify

F2/F3: Color