IXP1200 Network Processor Family ATM OC-3/12/Ethernet IP Router Example Design

Application Note 33

Modified on: 3/20/02,

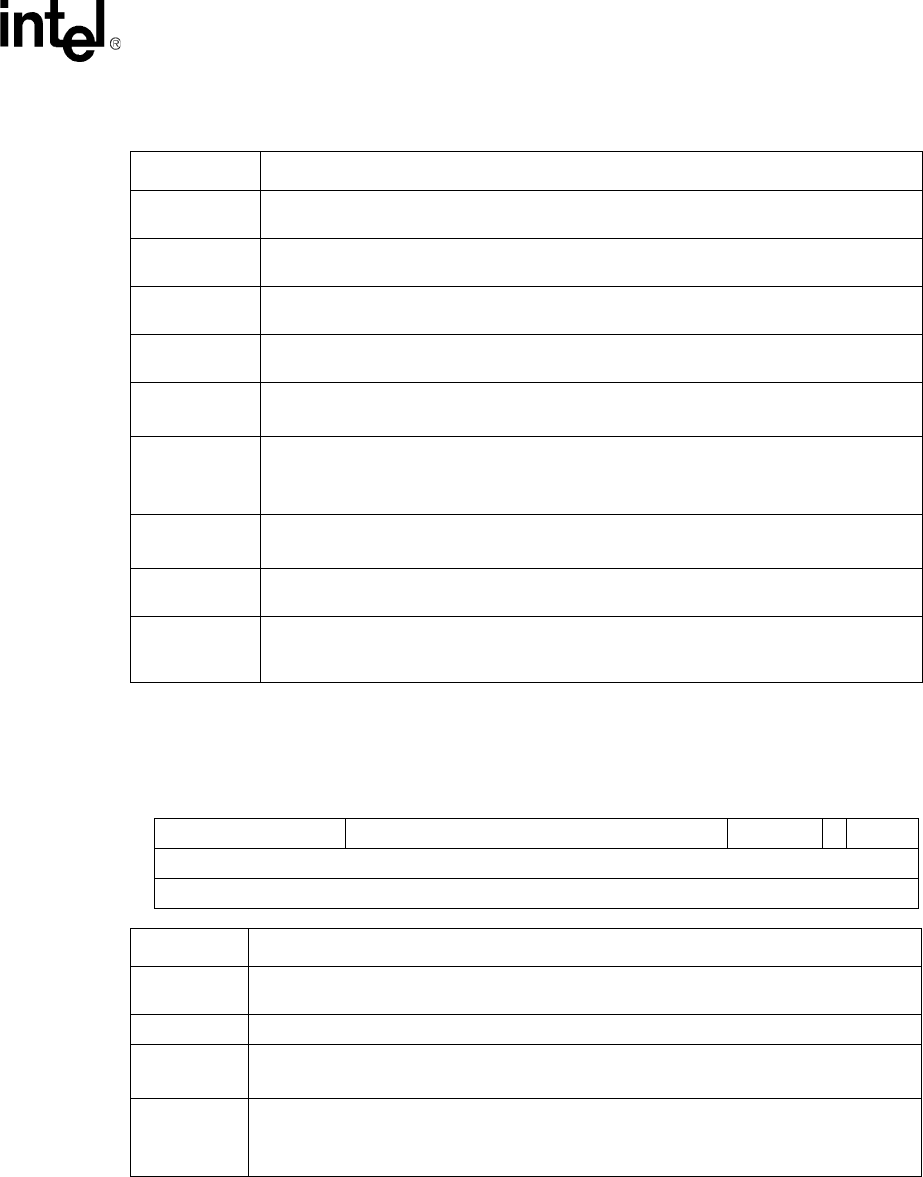

Entry Description

Next

Address of the next entry in the chain of entries that hash to the same row. 0 indicates no

next entry. (21 bit SRAM address)

Key

Hash key used to find this entry, also used to confirm arrival at the desired entry. Key =

(atm_header & 0xFFFFFFF0) | port#

Buffer Offset

Indicates which 64-bit DRAM word in the buffer should receive the next payload. On

completion of PDU assembly, this field is copied to the buffer descriptor.

Buffer Index

Buffer descriptor (and data buffer) to be used by ATM Receive to deposit payloads on this

VC.

LLC/SNAP

1: LLC0_IP, LLC1_IP

else: available for other patterns

Q

Queue To StrongARM core "Q" flag

1: queue all traffic to core

0: do not queue to core

AAL

5: ATM Adaptation Layer 5

0: VC is not open

CRC

The CRC-32 syndrome associated with the PDU. It is saved in the VC table entry after a cell

is moved, and then retrieved and used when the next cell in the PDU is received.

Cell Data11

The last four bytes of the previous cell in this PDU. Used during re-assembly of PDUs to

allow 8-byte quadword burst writes to DRAM without using DRAM Read/Modify/Write

instructions.

Figure 24. VC Lookup Table Entry (VC_TABLE_LINEAR)

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

9876543210

0 Buffer Offset Buffer Index LLC/SNAP Q AAL

1CRC

2 Cell data11

Entry Description

Buffer Offset

Indicates which 64-bit DRAM word in the buffer should receive the next payload. On

completion of PDU assembly, this field is copied to the buffer descriptor.

Buffer Index Buffer descriptor (and data buffer) to be used by ATM Receive to deposit payloads on this VC.

LLC/SNAP

1: LLC0_IP, LLC1_IP

else: available for other patterns

Q

Queue To StrongARM core "Q" flag

1: queue all traffic to core

0: do not queue to core