IXP1200 Network Processor Family ATM OC-3/12/Ethernet IP Router Example Design

Application Note 41

Modified on: 3/20/02,

4.4.3 System Limit on Packet Buffers

Several factors are involved in the number of packet buffers the system can support:

• The Ethernet transmitter uses packetqs (packetq.uc), and the implementation of packetqs can

address only 16,000 different buffers.

• DRAM capacity used = 2KB/buffer * number of buffers. Therefore, for 16,000 buffers, 32MB

of DRAM is consumed, which is half the memory capacity of most baseboards. (DRAM

capacity used by packet buffers can be crunched by reducing the buffer size to just fit a 1500

byte MTU. (2KB is overkill for this, but a handy power of 2), as well as enhancing the design

to also supporting small data buffers to hold small packets).

• SRAM capacity used = 16B * number of buffers. Therefore, for 16,000 buffers only 256KB of

SRAM is used, vs. an 8MB SRAM capacity.

4.5 Sequence Numbers - sequence.uc

Intra-microengine register-based sequence numbers are supplied by sequence.uc, and are used

extensively throughout the ATM portion of this design. This example employs a single-

microengine fast port receiver and so unlike other designs, it has no use for the global hardware

enqueue sequence number registers. ATM Receive has intersecting sequence numbers to de-couple

RFIFO receive order, VC cache/table lookup, and msgq_send(). ATM Transmit has sequence

numbers to decouple cell within a PDU order from TFIFO validate order. On the IXP1200 software

CRC microengine, sequence numbers are used to maintain PDU order within a VC.

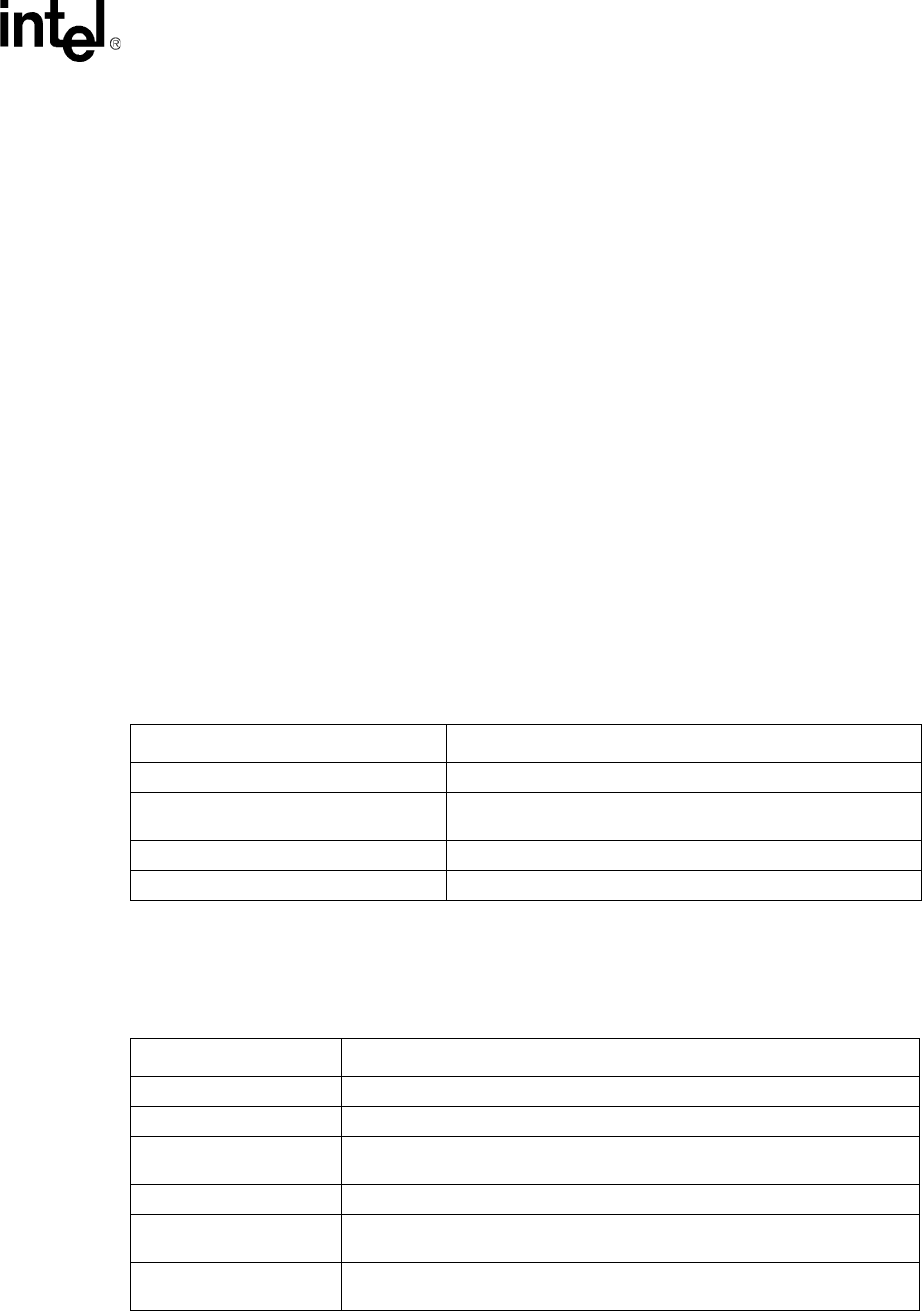

sequence.uc contains the following API calls:

4.5.1 SEQUENCE_HANDLE Usage

All sequence.uc calls use the same parameters. For convenience, a handle is typically defined and

used for all of the calls, as shown in the example below.

API Call Description

sequence_init(SEQUENCE_HANDLE) Initialize global state for the sequence number.

sequence_enter(SEQUENCE_HANDLE)

Increment absolute enter sequence number, and return that

number in a relative GPR.

sequence_wait(SEQUENCE_HANDLE) Wait until exit sequence number is equal to mine.

sequence_exit(SEQUENCE_HANDLE) Increment exit sequence number and continue.

Parameter Description

in_my_seq Relative GPR to hold sequence number for this thread.

in_enter Absolute GPR to hold ENTER sequence for all threads.

in_enter_inc

A register containing the value 1, or the constant 1. Register gives highest

performance.

io_exit Absolute GPR to hold the EXIT sequence for all threads.

in_exit_inc

A register containing the value 1, or the constant 1 Register gives highest

performance.

NUM_BITS

Number of bits in the sequence number. Must be a power of 2, from 1 to 32

inclusive. 32 is highest performance.