IXP1200 Network Processor Family ATM OC-3/12/Ethernet IP Router Example Design

38 Application Note

Modified on: 3/20/02,

4.4 SRAM Buffer Descriptors and DRAM Data Buffers

SRAM Buffer Descriptors and DRAM Data Buffers are a fundamental component of this design.

Each descriptor occupies 16 bytes of SRAM, and is used as a handle to describe and manage the

buffer. Each data buffer occupies 2K bytes of DRAM and holds the PDU payloads.

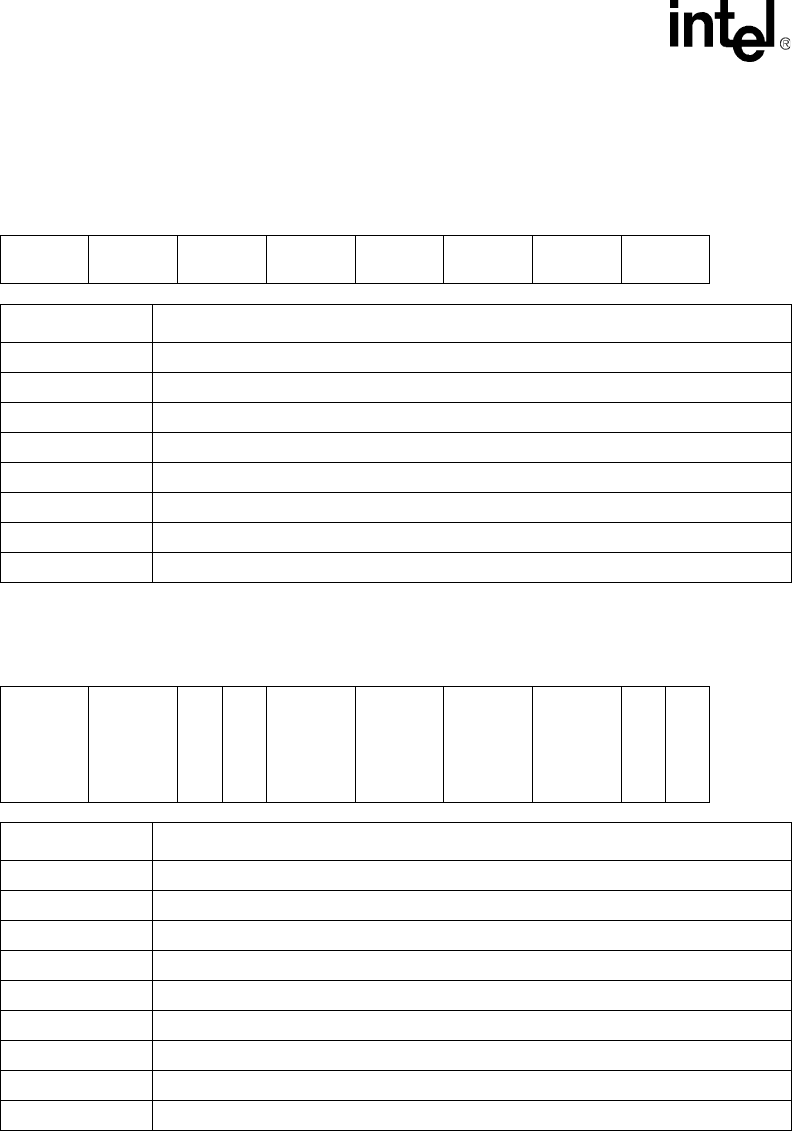

Figure 25. IP Route Table Entry - ATM Destination

0123456789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Bytes ->

ATM Bit +

MTU

Queue

Index

ATM

Header

IP Dest IP Mask

IP

Gateway

LLC High LLC Low

Entry Description

ATM bit + MTU 0x80000000 | MTU

Queue Index queue index (16 bits)

ATM Header ATM header for this VC, sans PTI bits

IP Dest IP destination address (32 bits)

IP mask IP subnet mask (32 bits)

IP Gateway IP next hop gateway (32 bits)

LLC High upper 32 bits of LLC/SNAP header

LLC Low lower 32 bits of LLC/SNAP header

Figure 26. IP Route Table Entry - Ethernet Destination

0123456789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Bytes ->

ITF

MAC DA

(0-3)

0

MAC DA (4,5)

IP Dest IP Mask

IP

Gateway

MAC SA

(0-3)

MAC SA (4,5)

MTU

Entry Description

ITF Output interface (32 bits).

MAC DA 0-3 Upper 32 bits of the destination MAC address.

MAC DA 4-5 Lower 16 bits of the destination MAC address.

IP Dest IP destination address (32 bits).

IP Mask IP subnet mask (32 bits)

IP Gateway IP next hop gateway (32 bits).

MAC SA 0-3 Upper 16 bits of this gateway’s source MAC address.

MAC SA (4,5)

Lower 32 bits of this gateway’s source MAC address.

MTU Maximum packet size.