TFX12V Power Supply Design Guide

Thin Form Factor with 12 V Connector

Version 2.0

20

2.2.9 Capacitive Load

The power supply should be able to power up and operate with the regulation limits defined in Table 2,

Section 2.2.1, with the following capacitances simultaneously present on the DC outputs.

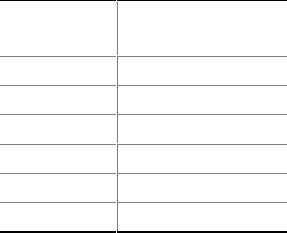

Table 12. Output Capacitive Loads

Output Capacitive Load

(PF)

+12 V1DC 5,000

+12 V2DC 3,000

+5 VDC 10,000

+3.3 VDC 6,000

-12 VDC 350

+5 VSB 350

2.2.10 Closed-loop Stability

The power supply shall be unconditionally stable under all line/load/transient load conditions including

capacitive loads specified in Section 2.2.9. A minimum of 45 degrees phase margin and 10 dB gain margin is

recommended at both the maximum and minimum loads.

2.2.11 +5 VDC / +3.3 VDC Power Sequencing

The +12 VDC and +5 VDC output levels must be equal to or greater than the +3.3 VDC output at all times

during power-up and normal operation. The time between the +12 VDC or +5 VDC output reaching its

minimum in-regulation level and +3.3 VDC reaching its minimum in-regulation level must be ≤ 20 ms.

2.2.12 Voltage Hold-up Time

The power supply should maintain output regulations per Section 2.2.1 despite a loss of input power at the

low-end nominal range—115 VAC / 57 Hz or 230 VAC / 47 Hz - at maximum continuous output load as

applicable for a minimum of 17 ms.