Chapter 4 Signal Connections

PCI-6023E/6024E/6025E User Manual 4-38

©

National Instruments Corporation

A counter on your board internally generates the STARTSCAN signal

unless you select some external source. This counter is started by the

TRIG1 signal and is stopped either by software or by the sample counter.

Scans generated by either an internal or external STARTSCAN signal are

inhibited unless they occur within a DAQ sequence. Scans occurring within

a DAQ sequence may be gated by either the hardware (AIGATE) signal or

software command register gate.

CONVERT* Signal

Any PFI pin can externally input the CONVERT* signal, which is

available as an output on the PFI2/CONVERT* pin.

Refer to Figures 4-17 and 4-18 for the relationship of CONVERT* to the

DAQ sequence.

As an input, the CONVERT* signal is configured in the edge-detection

mode. You can select any PFI pin as the source for CONVERT* and

configure the polarity selection for either rising or falling edge. The

selected edge of the CONVERT* signal initiates an A/D conversion.

The ADC switches to hold mode within 60 ns of the selected edge. This

hold-mode delay time is a function of temperature and does not vary from

one conversion to the next. CONVERT* pulses should be separated by at

least 5 µs (200 kHz sample rate)

As an output, the CONVERT* signal reflects the actual convert pulse that

is connected to the ADC. This is true even if the conversions are being

externally generated by another PFI. The output is an active low pulse with

a pulse width of 50 to 150 ns. This output is set to tri-state at startup.

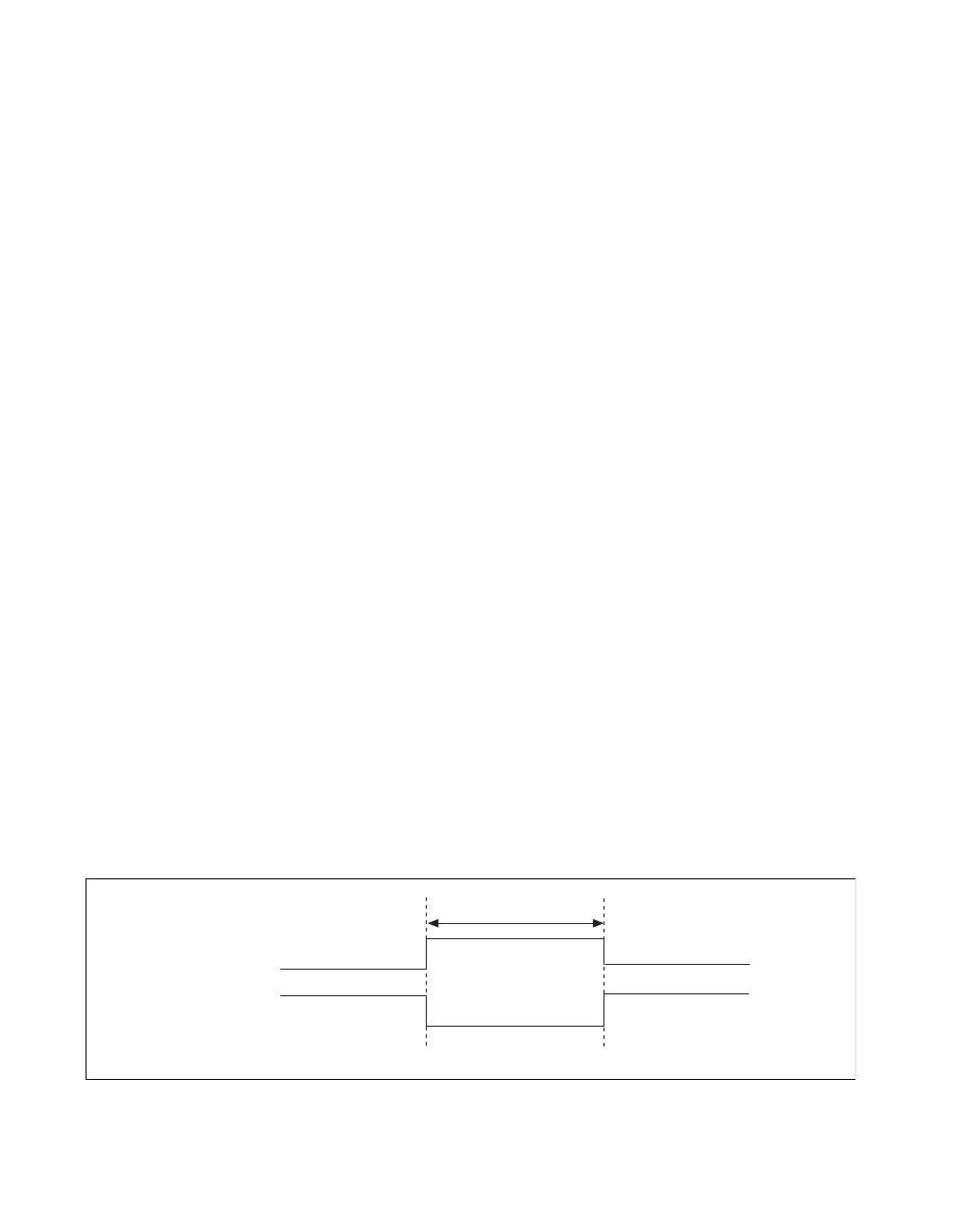

Figures 4-27 and 4-28 show the input and output timing requirements for

the CONVERT* signal.

Figure 4-27.

CONVERT* Input Signal Timing

Rising-edge

polarity

Falling-edge

polarity

t

w

t

w

= 10 ns minimum

PCI.book Page 38 Wednesday, September 16, 1998 9:09 AM