219

CHAPTER 8 16-BIT TIMER/EVENT COUNTER

8.6 16-Bit Timer/Event Counter Operating Precautions

(1) Timer start errors

An error with a maximum of one clock may occur concerning the time required for a match signal to be

generated after timer start. This is because the 16-bit timer register (TM0) is started asynchronously with

the count pulse.

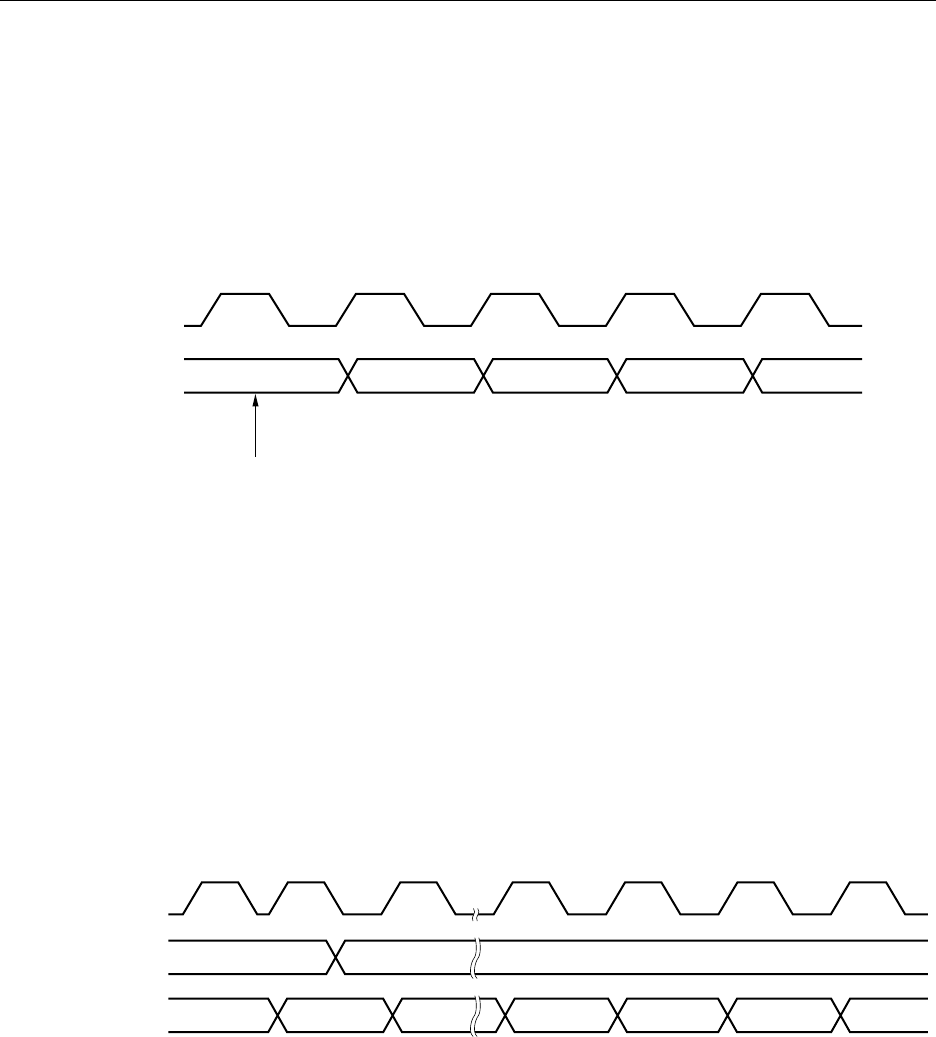

Figure 8-35. 16-Bit Timer Register Start Timing

(2) 16-bit compare register setting

Set a value other than 0000H to the 16-bit capture/compare register 00 (CR00).

Thus, when using the 16-bit capture/compare register as event counter, one-pulse count operation cannot

be carried out.

(3) Operation after compare register change during timer count operation

If the value after the 16-bit capture/compare register (CR00) is changed is smaller than that of the 16-bit

timer register (TM0), TM0 continues counting, overflows and then restarts counting from 0. Thus, if the value

(M) after CR00 change is smaller than that (N) before change, it is necessary to restart the timer after

changing CR00.

Figure 8-36. Timings After Change of Compare Register During Timer Count Operation

Remark N > X > M

Timer Start

Count Pulse

TM0 Count Value 0000H 0001H 0002H 0003H 0004H

Count Pulse

CR00 Captured Value

TM0 Count Value X – 1 X FFFFH 0000H 0001H 0002H

MN