348

CHAPTER 17 SERIAL INTERFACE CHANNEL 0 (

µ

PD78078 SUBSERIES)

Table 17-3. Various Signals in SBI Mode (1/2)

Timing Chart

Definition

Signal Name

Output

Device

Output

Condition

Effects on Flag Meaning of Signal

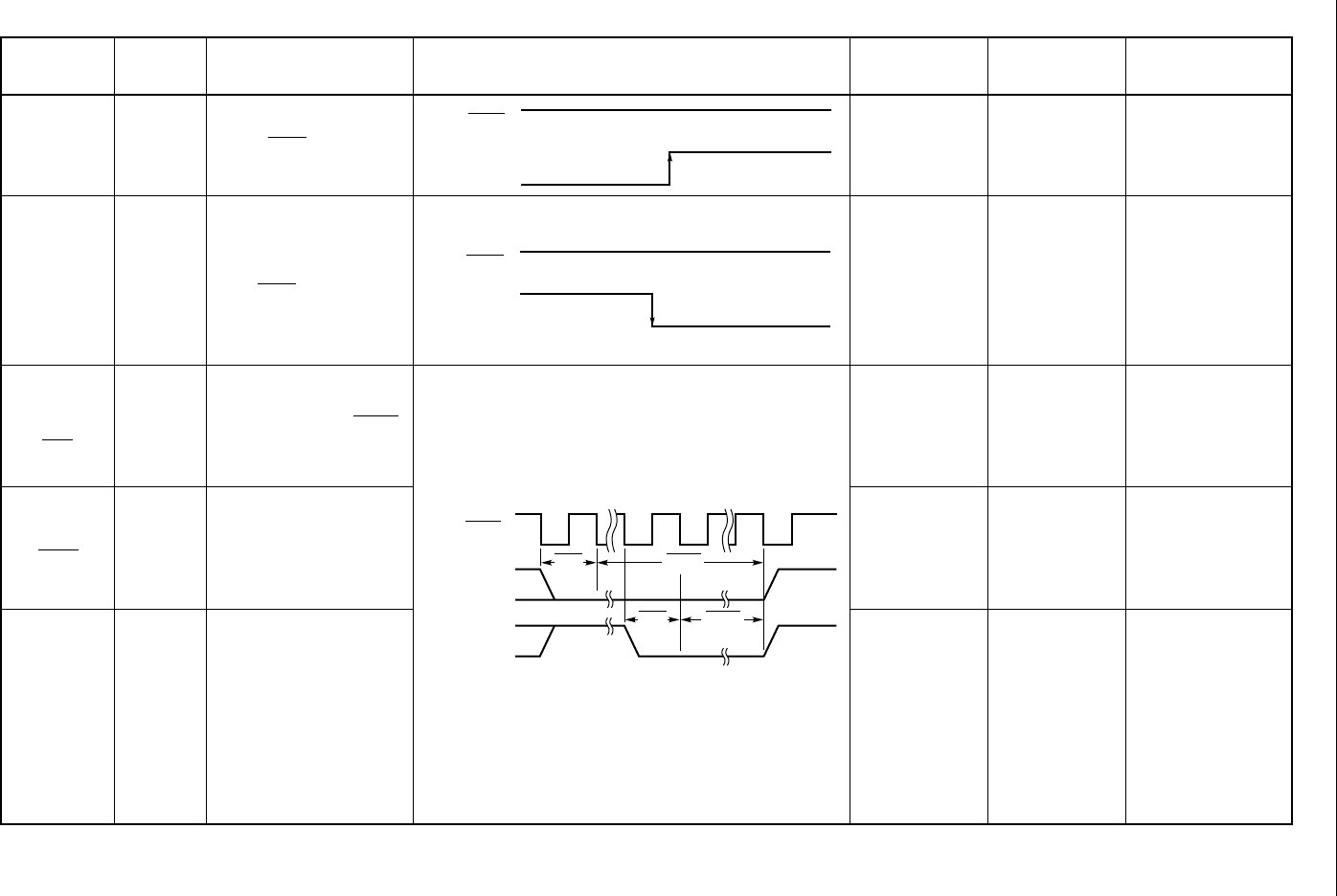

CMD signal is output

to indicate that

transmit data is an

address.

i) Transmit data is an

address after REL

signal output.

ii) REL signal is not

output and trans-

mit data is an

command.

Low-level signal to be

output to SB0 (SB1) during

one-clock period of SCK0

after completion of serial

reception

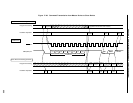

[Synchronous BUSY signal]

Low-level signal to be

output to SB0 (SB1)

following Acknowledge

signal

(1) BSYE = 0

(2) Execution of

instruction for

data write to

SIO0

(transfer start

instruction)

Master/

slave

SB0 (SB1) rising edge

when SCK0 = 1

Master

Bus release

signal

(REL)

• RELT set

• RELD set

• CMDD clear

• CMDD set

• CMDT set

Master

Command

signal

(CMD)

SB0 (SB1) falling edge

when SCK0 = 1

Acknowledge

signal

(ACK)

(1) ACKE = 1

(2) ACKT set

• ACKD set

Completion of

reception

Slave

Busy signal

(BUSY)

• BSYE = 1 —

Serial receive disable

because of

processing

—

Serial receive enable

Slave

Ready signal

(READY)

High-level signal to be

output to SB0 (SB1)

before serial transfer start

and after completion of

serial transfer

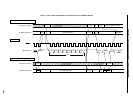

[Synchronous BUSY output]

SCK0

D0 READY

SB0 (SB1)

D0 READY

SB0 (SB1)

ACK BUSY

BUSYACK

9

SCK0

“H”

SB0 (SB1)

“H”

SB0 (SB1)

SCK0