496

CHAPTER 21 REAL-TIME OUTPUT PORT

(1) Real-time output buffer register (RTBL, RTBH)

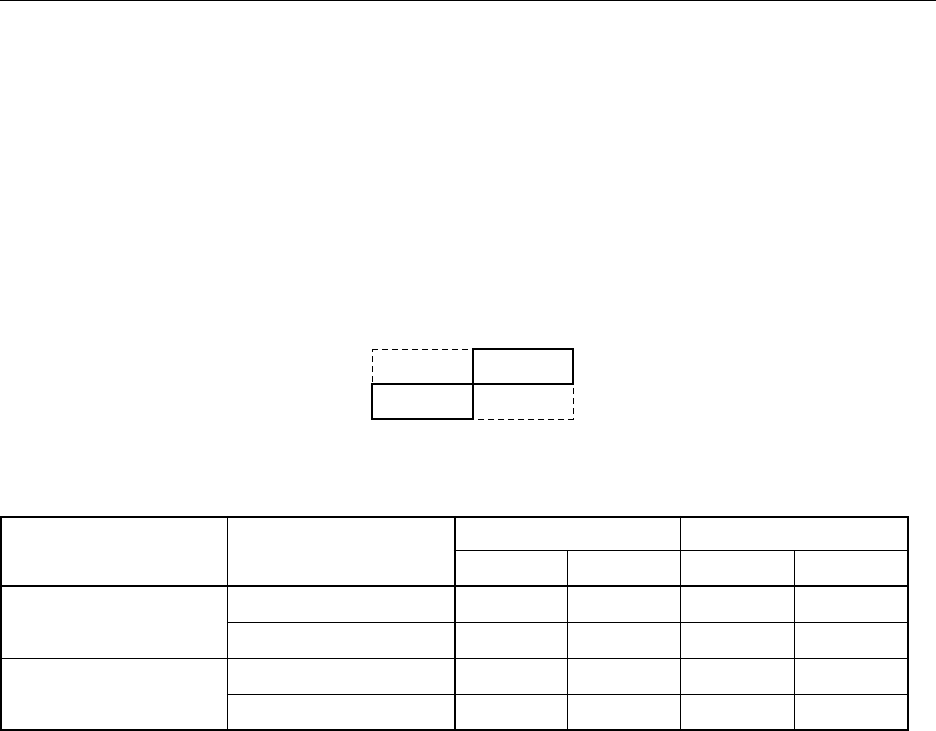

Addresses of RTBL and RTBH are mapped individually in the special function register (SFR) area as shown

in Figure 21-2.

When specifying 4 bits x 2 channels as the operating mode, data are set individually in RTBL and RTBH.

When specifying 8 bits x 1 channel as the operating mode, data are set to both RTBL and RTBH by writing

8-bit data to either RTBL or RTBH.

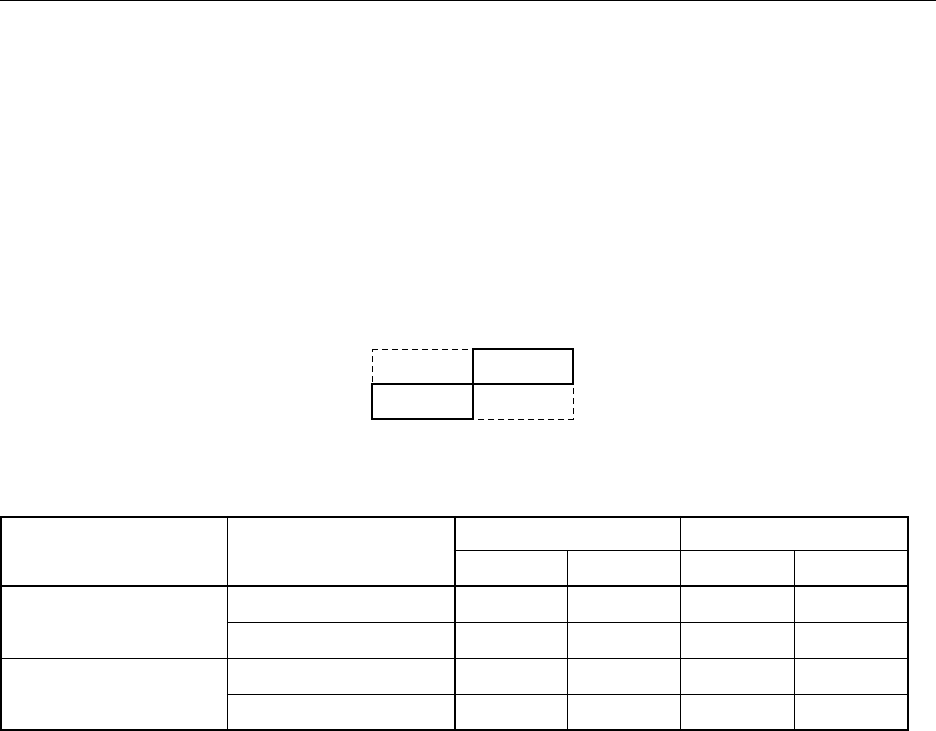

Table 21-2 shows operations during manipulation of RTBL and RTBH.

Figure 21-2. Real-time Output Buffer Register Configuration

Table 21-2. Operation in Real-time Output Buffer Register Manipulation

In Read

Note 1

In Write

Note 2

Higher 4 Bits Lower 4 Bits Higher 4 Bits Lower 4 Bits

RTBL RTBH RTBL Invalid RTBL

RTBH RTBH RTBL RTBH Invalid

RTBL RTBH RTBL RTBH RTBL

RTBH RTBH RTBL RTBH RTBL

Notes 1. Only the bits set in the real-time output port mode can be read. When a read is performed to the bits

set in the port mode, 0 is read out.

2. After setting data in the real-time output port, output data should be set in RTBL and RTBH by the

time a real-time output trigger is generated.

Higher

4 Bits

Lower

4 Bits

RTBL

RTBH

FF30H

FF31H

Operating Mode

Register to be

Manipulated

4 Bits x 2 Channels

8 Bits x 1 Channel