31

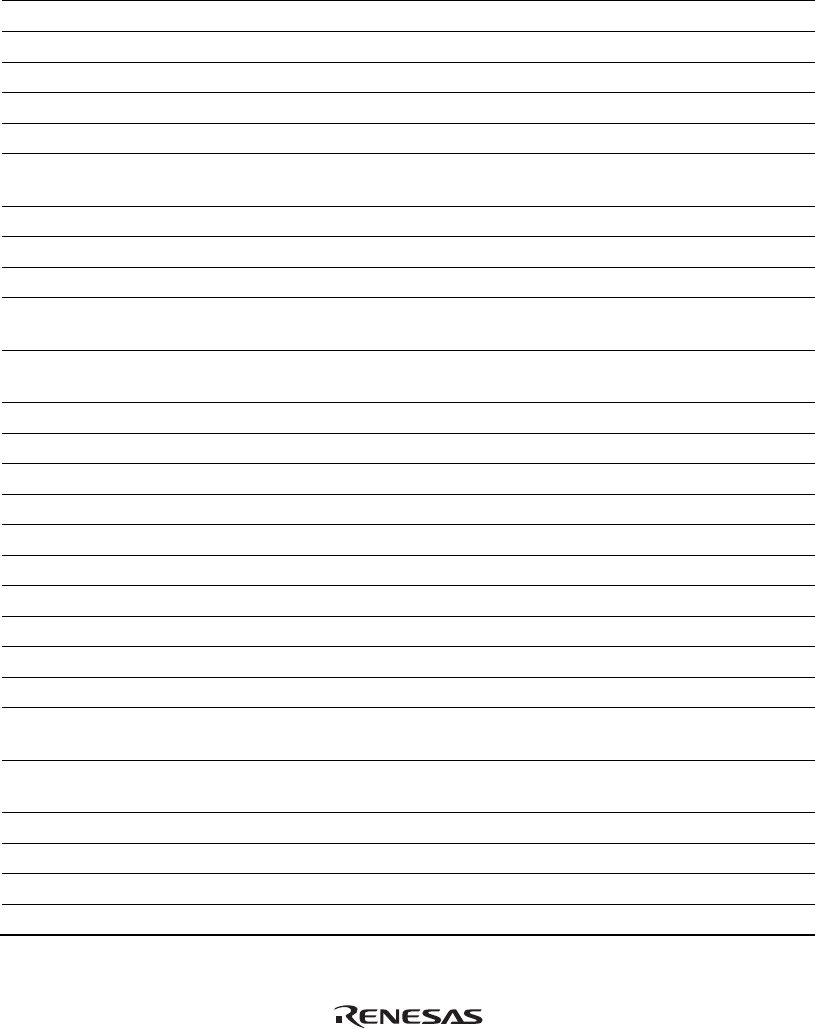

Table 2.10 Measurement Item

Selected Name Option

Disabled None

Elapsed time AC

Number of execution states VS

Branch instruction counts BT

Number of execution instructions I

DSP-instruction execution counts DI (Devices incorporating the DSP function can

only be measured.)

Instruction/data conflict cycle MAC

Other conflict cycles than instruction/data OC

Exception/interrupt counts EA

Data-TLB miss cycle MTS (Devices incorporating the MMU function

can only be measured.)

Instruction-TLB miss cycle ITS (Devices incorporating the MMU function

can only be measured.)

Interrupt counts INT

Number of BL=1 instructions BL1

Number of MD=1 instructions MD1

Instruction cache-miss counts IC

Data cache-miss counts DC

Instruction fetch stall IF

Data access stall DA

Instruction cache-miss stall ICS

Data cache-miss stall DCS

Cacheable access stall CS

X/Y-RAM access stall XYS (Devices incorporating the X/Y memory

can only be measured.)

URAM access stall US (Devices incorporating the U memory can

only be measured.)

Instruction/data access stall cycle MA

Other access cycles than instruction/data NMA

Non-cacheable area access cycle NCC

Non-cacheable area instruction access cycle NCI