Si53xx-RM

Rev. 0.5 25

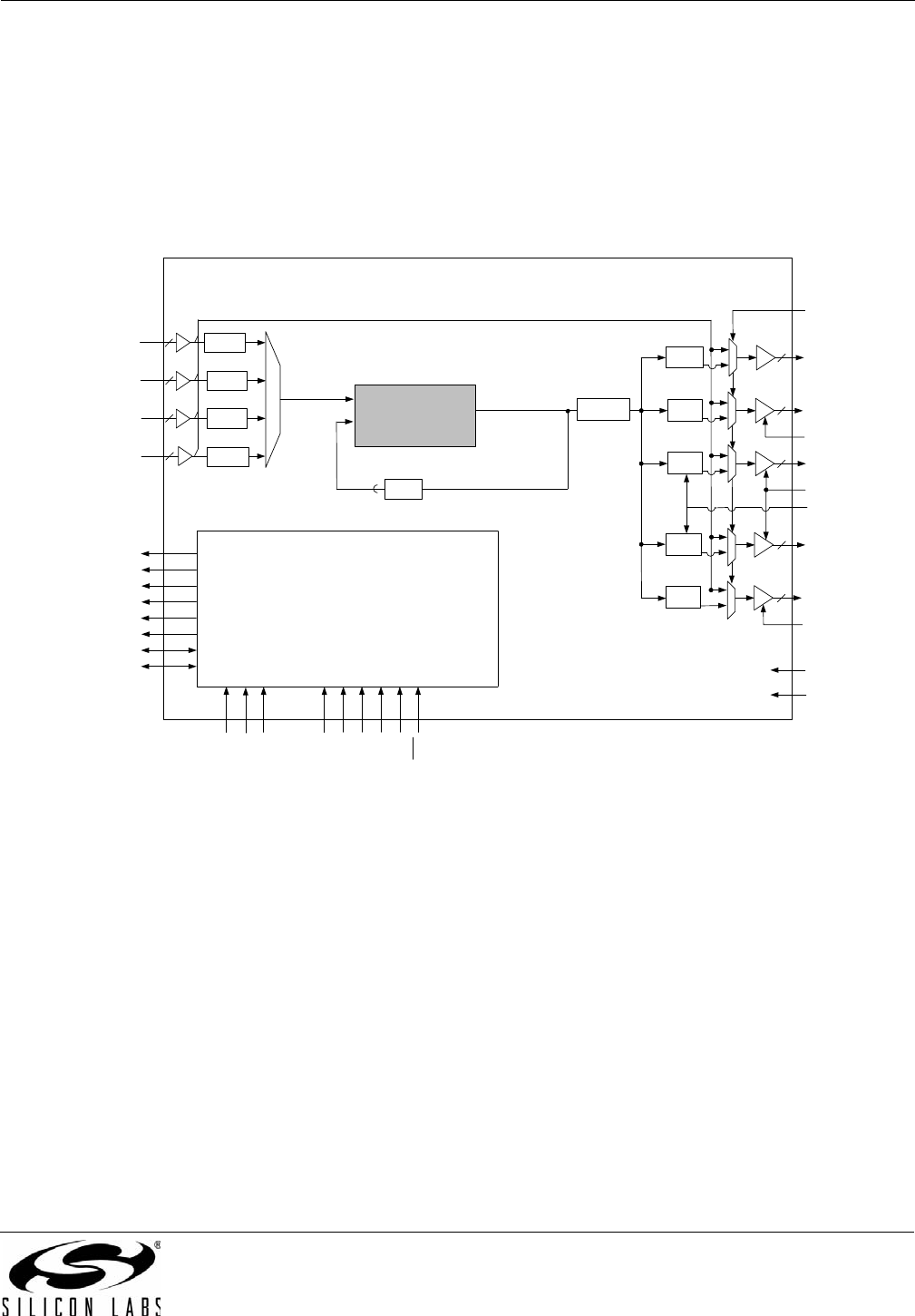

3.9. Si5365

The Si5365 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5365 accepts four clock inputs ranging from 19.44 MHz to 707 MHz and generates five

frequency-multiplied clock outputs ranging from 19.44 MHz to 1050 MHz. The input clock frequency and clock

multiplication ratio are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video

rates. The DSPLL loop bandwidth is digitally selectable. Operating from a single 1.8, 2.5 V, or 3.3 V supply, the

Si5365 is ideal for providing clock multiplication in high performance timing applications. See "6. Pin Control Parts

(Si5316, Si5322, Si5323, Si5365, Si5366)" on page 50 for a complete description.

Figure 9. Si5365 Low Jitter Clock Multiplier Block Diagram

C2A

CS0_C3A

C2B

CS1_C4A

ALRMOUT

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

f

3

DBL2_BY

DBL34

DBL5

BWSEL[1:0]

FRQSEL[3:0]

DIV34[1:0]

FOS_CTL

SFOUT[1:0]

RST

CMODE

AUTOSEL

BYPASS/

DSBL2

Control

÷ N3_2

÷ N3_1

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

FRQTBL

DIV34[1:0]

÷ N1_HS

DSPLL

®

÷ N2