Si53xx-RM

46 Rev. 0.5

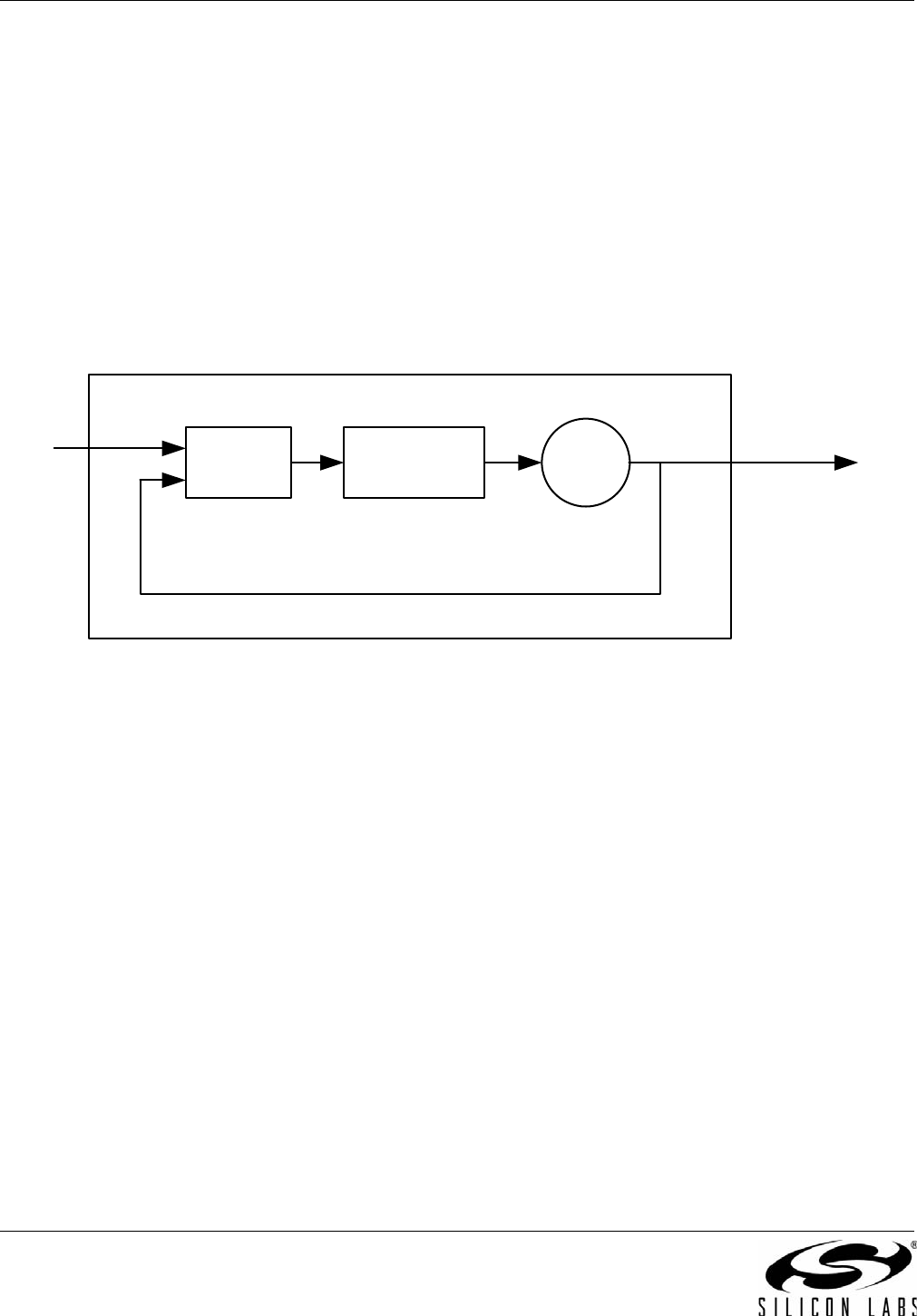

5. DSPLL (All Devices)

All members of the Any-Frequency Precision Clocks family incorporate a phase-locked loop (PLL) that utilizes

Silicon Laboratories' third generation DSPLL technology to eliminate jitter, noise, and the need for external VCXO

and loop filter components found in discrete PLL implementations. This is achieved by using a digital signal

processing (DSP) algorithm to replace the loop filter commonly found in discrete PLL designs. Because external

PLL components are not required, sensitivity to board-level noise sources is minimized. This digital technology

provides highly stable and consistent operation over process, temperature, and voltage variations.

A simplified block diagram of the DSPLL is shown in Figure 20. This algorithm processes the phase detector error

term and generates a digital frequency control word M to adjust the frequency of the digitally-controlled oscillator

(DCO). The narrowband configuration devices (Si5316, Si5319, Si5323, Si5324, Si5326, Si5327, Si5366, Si5368,

and Si5369) provide ultra-low jitter generation by using an external jitter reference clock and jitter attenuation. For

applications where basic frequency multiplication of low jitter clocks is all that is required, the wideband parts

(Si5322, Si5325, Si5365, and Si5367) are available.

Figure 20. Any-Frequency Precision Clock DSPLL Block Diagram

f

IN

DSPLL

Phase

Detector

Digital

DCO

Digital Loop

Filter

Fvco

M

f

OUT