Si53xx-RM

48 Rev. 0.5

5.2. PLL Performance

All members of the Any-Frequency Precision Clock family of devices provide extremely low jitter generation, a well-

controlled jitter transfer function, and high jitter tolerance. For more information the loop bandwidth and its effect on

jitter attenuation, see "Appendix H—Jitter Attenuation and Loop BW" on page 164.

5.2.1. Jitter Generation

Jitter generation is defined as the amount of jitter produced at the output of the device with a jitter free input clock.

Generated jitter arises from sources within the VCO and other PLL components. Jitter generation is a function of

the PLL bandwidth setting. Higher loop bandwidth settings may result in lower jitter generation, but may result in

less attenuation of jitter that might be present on the input clock signal.

5.2.2. Jitter Transfer

Jitter transfer is defined as the ratio of output signal jitter to input signal jitter for a specified jitter frequency. The

jitter transfer characteristic determines the amount of input clock jitter that passes to the outputs. The DSPLL

technology used in the Any-Frequency Precision Clock devices provides tightly controlled jitter transfer curves

because the PLL gain parameters are determined largely by digital circuits which do not vary over supply voltage,

process, and temperature. In a system application, a well-controlled transfer curve minimizes the output clock jitter

variation from board to board and provides more consistent system level jitter performance.

The jitter transfer characteristic is a function of the loop bandwidth setting. Lower bandwidth settings result in more

jitter attenuation of the incoming clock, but may result in higher jitter generation. Section 1 Any-Frequency

Precision Clock Product Family Overview also includes specifications related to jitter bandwidth and peaking.

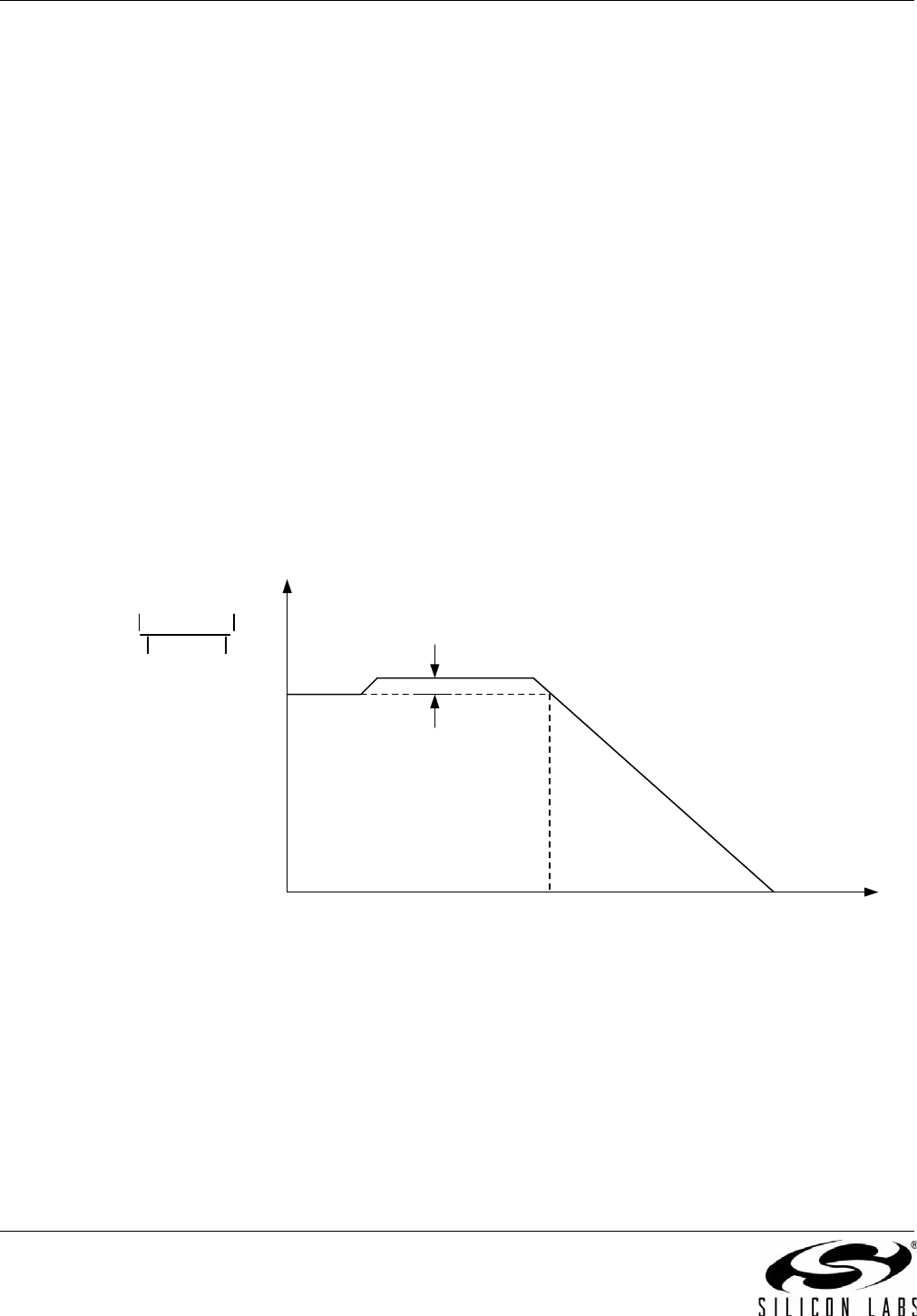

Figure 22 shows the jitter transfer curve mask.

Figure 22. PLL Jitter Transfer Mask/Template

Jitter

Transfer

0 dB

BW

f

Jitter

Peaking

–20 dB/dec.

Jitter Out

Jitter In

)

(

20 x LOG