Motherboard Description SY-7ISA+

10

1-6.5 Multiplexed AGP and Display Cache Interface

The Intel® 815E GMCH multiplexes an AGP interface with a

display cache interface for internal 3D graphics performance

improvement. The Display Cache is used only in the internal

graphics. When an AGP card is installed in the system, the Intel®

815E GMCH internal graphics will be disabled and the AGP

controller will be enabled.

1-6.5.1 AGP Interface

A single AGP connector is supported by the Intel® 815E GMCH

AGP interface. The AGP buffers operate in one of two selectable

modes in one of two selectable modes in order to support the AGP

Universal Connector:

1) 3.3V drive, not 5 volt safe – This mode is compliant to the AGP

1.0 and 2.0 specs.

2) 1.5V drive, not 3.3 volt safe – This mode is compliant with the

AGP 2.0 spec.

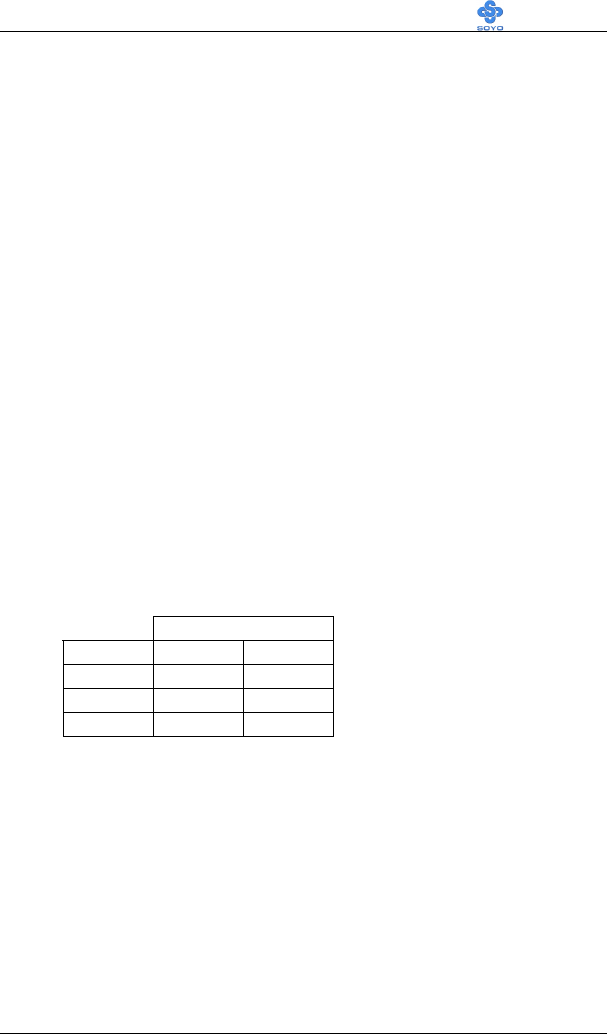

The following table shows the AGP Data Rate and the Signaling

Levels supported by the GMCH:

Signaling Level

Data Rate 1.5V 3.3V

1x AGP Yes Yes

2x AGP Yes Yes

4x AGP Yes No

The AGP interface supports 4x AGP signaling. AGP semantic

(PIPE# or SBA[7:0]) cycles to SDRAM are not snooped on the host

bus. AGP FRAME# cycles to SDRAM are snooped on the host bus.

The GMCH supports PIPE# or SBA[7:0] AGP address mechanisms,

but not both simultaneously. Either the PIPE# or the SBA[7:0]

mechanism must be selected during system initialization. High

priority accesses are supported. Only memory writes form the hub

interface to AGP are allowed. No transactions from AGP to the hub