USB 2.0 Hi-Speed 2-Port Hub Controller

Datasheet

Revision 1.96 (07-11-08) 26 SMSC USB2512A

DATASHEET

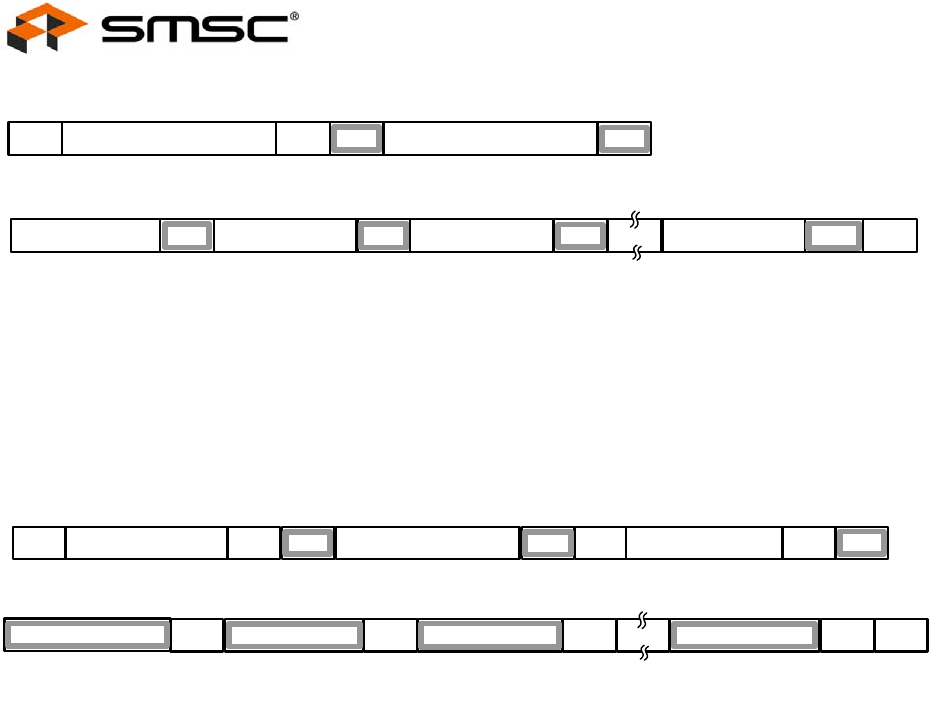

Figure 4.1 Block Write

Block Read

A Block Read differs from a block write in that the repeated start condition exists to satisfy the I

2

C

specification’s requirement for a change in the transfer direction.

Figure 4.2 Block Read

4.3.2 Invalid Protocol Response Behavior

Registers that are accessed with an invalid protocol are not updated. A register is only updated

following a valid protocol. The only valid protocols are Write Block and Read Block, which are

described above.

The Hub only responds to the hardware selected Slave Address.

Attempting to communicate with the Hub over SMBus with an invalid slave address or invalid protocol

results in no response, and the SMBus Slave Interface returns to the idle state.

The only valid registers that are accessible by the SMBus slave address are the registers defined in

the Registers Section. See Section 4.3.3 for the response to undefined registers.

4.3.3 General Call Address Response

The Hub does not respond to a general call address of 0000_000b.

4.3.4 Slave Device Time-Out

According to the SMBus Specification, V1.0 devices in a transfer can abort the transfer in progress

and release the bus when any single clock low interval exceeds 25ms (T

TIMEOUT, MIN

). Devices that

have detected this condition must reset their communication and be able to receive a new START

condition no later than 35ms (T

TIMEOUT, MAX

).

Note: Some simple devices do not contain a clock low drive circuit; this simple kind of device typically

resets its communications port after a start or stop condition. The Slave Device Time-Out must

be implemented.

181

S Slave Address Register AddressWr A

17118

A

1

...

Byte Count = N

A Data byte 1 A Data byte 2

81 1 188

Data byte N A P

Block Write

A

Block Read

1

SS Slave Address Register AddressWr A

17118

A

1

Slave Address Rd A

711

81 1 188

P

181

A AAA

Byte Count = N

Data byte 1 Data byte 2 Data byte N

...