Chapter 4 – SocketModem Parallel Interface – A Programmer’s Description

SocketModem Global MT5634SMI Developer’s Guide 19

RBR Receive Buffer (RX FIFO)

All eight bits are used for receive channel data (host read/data in; host write/data out). The three error bits per

byte are copied into bits 2, 3, and 4 of the LSR during each host I/O read; therefore, they are available for

monitoring on a per-byte basis.

THR Transmit Holding Register (TX FIFO)

All eight bits are used for transmit channel data (host write/data out; host read/data in).

IER Interrupt Enable

Bits 4–7: Reserved and will always read 0.

Bits 0-3: Set by host software only and cleared by software control or host reset.

Bit 3: Enables modem status IRQ. If bits 0–3 of the MSR are set and this bit is set to 1 (enabled), a host

interrupt is generated.

Bit 2: Enables receive line status IRQ. If bits 1–4 (overrun, parity, framing, break errors) of the LSR are

set and this bit is set to a logic 1, a host interrupt is generated.

Bit 1: Enables transmit holding register IRQ. If bit 5 (transmit holding register empty) of the LSR is set

and this bit is set to a 1, a host interrupt is generated.

Bit 0: Enables received data available IRQ. If bit 0 (data ready) of the LSR is set and this bit is set to a 1,

a host interrupt is generated.

IIR Interrupt Identification (Read Only)

Bits 6–7: (FIFO enabled bits). These bits will read a 1 if FIFO mode is enabled and the 16450 enable bit is 0

(no force of 16450 mode).

Bits 4–5: Reserved and always read a 0.

Bits 1–3: Interrupt ID bits.

Bit 0: Interrupt pending. If logic 0 (in default mode), an interrupt is pending.

When the host accesses IIR, the contents of the register are frozen. Any new interrupts will be recorded, but not

acknowledged during the IIR access. This requires buffering bits (0–3, 6–7) during IIR reads.

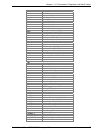

Bit 3 Bit 2 Bit 1 Priority Interrupt Source Interrupt Reset Control

011HighestOverrun, parity, framing, error

or break detect bits set by

SocketModem Controller

Reading the LSR

0102

nd

Received data trigger level RX FIFO drops below trigger

level

1102

nd

Receiver time-out with data in

RX FIFO

Read RX FIFO

0013

rd

TX holding register empty Writing to TX holding register

or reading IIR when TX

holding register is source of

error

0004

th

MODEM status: CTS, DSR,

RI or DCD

Reading the MSR