Texas Instruments 4Q 2006 Interface Selection Guide

PanelBus™ HDCP Digital Receiver

T

FP501, TFP503

Get datasheets at: www.ti.com/TFP501 or www.ti.com/TFP503

The TFP501 and TFP503 are TI PanelBus flat panel display products,

part of a comprehensive family of end-to-end DVI 1.0-compliant

solutions. The TFP501/TFP503 support display resolutions up to UXGA,

including the standard HDTV formats, in 24-bit true-color pixel format.

The TFP501/TFP503 offer design flexibility to drive one or two pixels

per clock, support TFT or DSTN panels and provide an option for

time-staggered pixel outputs for reduced ground-bounce.

Key Features

• Supports UXGA resolution (output pixel rates up to 165 MHz)

• Digital visual interface (DVI) and high-bandwidth digital content

protection (HDCP) specification compliant

•

Encrypted external HDCP device key storage for exceptional security

and ease of implementation

• True color, 24 bits/pixel, 48-bit dual-pixel output mode;

16.7/M colors at one or two pixels per clock

• 4x oversampling for reduced bit-error rates and better performance

over longer cables

• Embedded HDCP keys (TFP503 only)

• Supports hot-plug detection

• Packaging: 100-pin TQFP PowerPAD™

Applications

• Desktop LCD monitors

• DLP

®

and LCD projectors

• Digital TVs

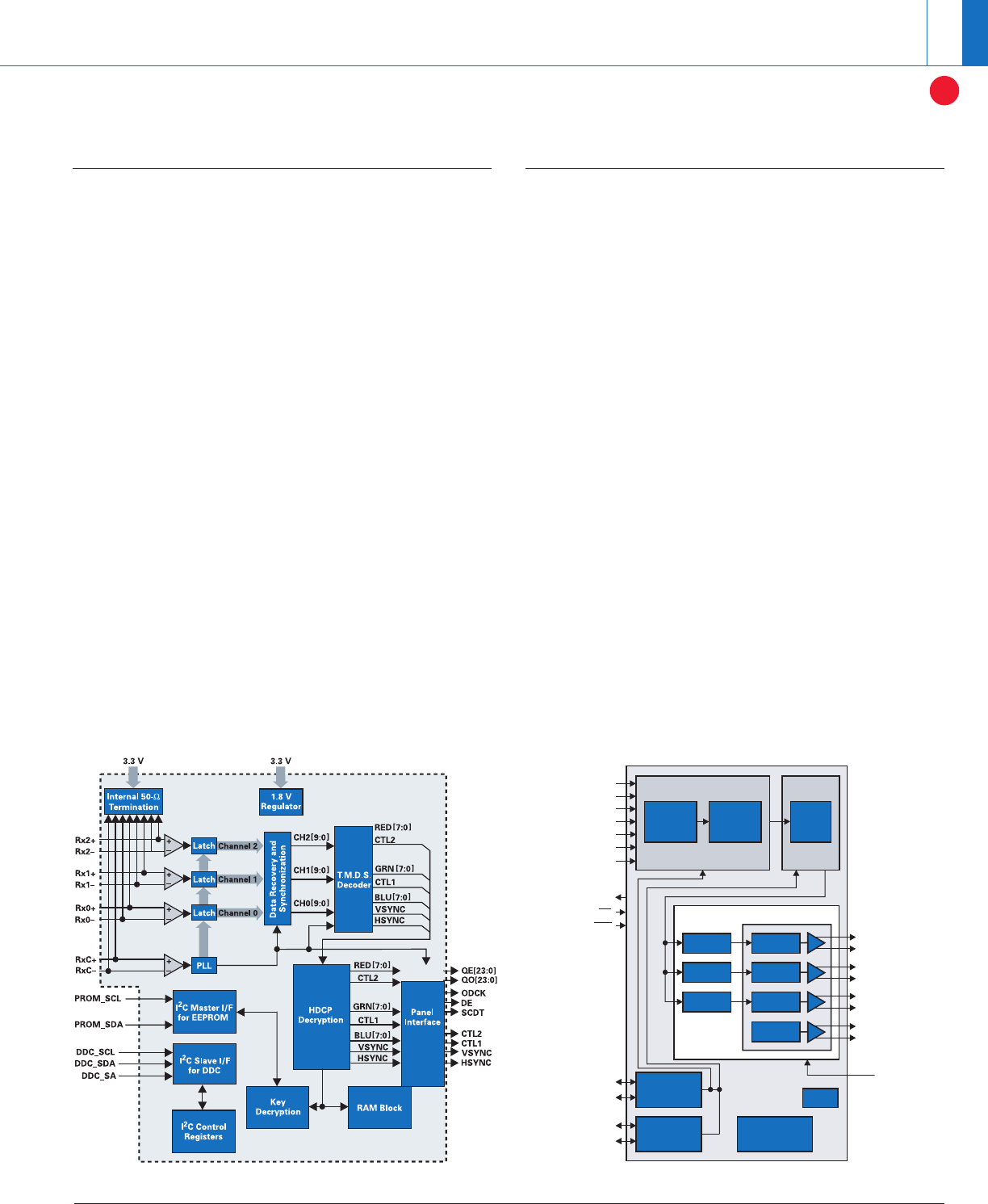

TFP501 block diagram.

TI PanelBus™ Digital Transmitters

T

FP510, TFP513

Get the datasheets and app reports at: www.ti.com/sc/device/TFP510 or

www.ti.com/sc/device/TFP513

The TFP510 and TFP513 provide a universal interface allowing a glue-

less connection to most commonly available graphics controllers. Some

of the advantages of this universal interface include selectable bus

widths, adjustable signal levels and differential and single-ended

clocking. The DVI interface supports flat panel display resolutions up

to UXGA at 165 MHz in 24-bit true color pixel format.

Key Features

• Digital visual interface (DVI) compliant

• Supports resolutions from VGA to UXGA

(25-MHz to 165-MHz pixel rates)

• Universal graphics controller interface

••

12-bit, dual-edge and 24-bit, single-edge input modes

••

Adjustable 1.1-V to 1.8-V and standard 3.3-V CMOS input signal

levels

••

Fully differential and single-ended input clocking modes

••

Standard Intel

®

12-bit digital video port compatible as on Intel

81x chipsets

• Programmable using I

2

C serial interface

• Monitor detection through hot-plug and receiver detection

• Embedded HDCP keys (TFP513 only)

• Packaging: 64-pin TQFP PowerPAD™

Applications

• Set-top boxes

• DVD recorders/players

TFP510 block diagram.

T.M.D.S.Transmitter

TX2

TX1

TX0

TXC

TFADJ

IDCK

DATA[23:0]

DE

VSYNC

HSYNC

EDGE/

HTPLG

MSEN

BSEL/SCL

DSEL/SDA

V

REF

MDA/DK2

MCL/DK1

ISEL/RST

PD

Serializer

Serializer

Serializer

Control

Encoder

Encoder

Encoder

IC Slave I/F

2

For DDC

1.8-V Regulators

with Bypass

Capacitors

PLL

for EEPROM

IC Master I/F

2

Universal Input

HDCP

Encryption

12-/24-Bit

I/F

Data

Format

HDCP

Cipher

DVI/PanelBus

™

23

➔